C-3

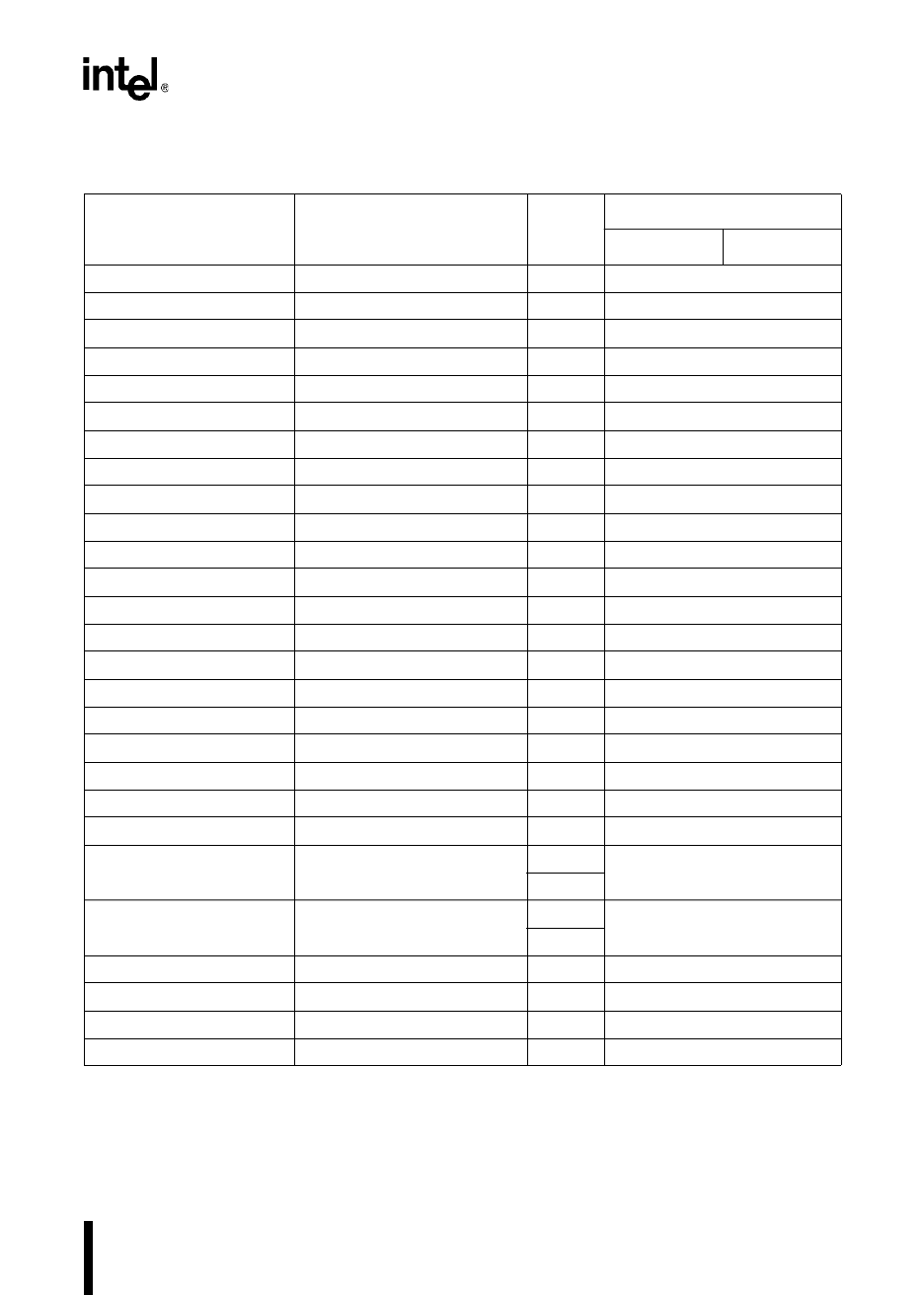

REGISTERS

EPA1_TIME EPA Capture/Comp 1 Time 1F46 XXXX XXXX XXXX XXXX

EPA2_TIME (MC, MD) EPA Capture/Comp 2 Time 1F4A XXXX XXXX XXXX XXXX

EPA3_TIME (MC, MD) EPA Capture/Comp 3 Time 1F4E XXXX XXXX XXXX XXXX

EPA4_TIME (MD) EPA Capture/Comp 4 Time 1F52 XXXX XXXX XXXX XXXX

EPA5_TIME (MD) EPA Capture/Comp 5 Time 1F56 XXXX XXXX 0000 0000

FREQ_CNT (MD) Frequency Gen Count 1FBA 0000 0000

FREQ_GEN (MD) Frequency 1FB8 0000 0000

GEN_CON (MH) General Configuration 1FA0 0000 0000

INT_MASK Interrupt Mask 0008 0000 0000

INT_MASK1 Interrupt Mask 1 0013 0000 0000

INT_PEND Interrupt Pending 0009 0000 0000

INT_PEND1 Interrupt Pending 1 0012 0000 0000

ONES_REG Ones Register 0002 1111 1111 1111 1111

P1_DIR (MH) Port 1 I/O Direction 1F9B 1111 1111

P2_DIR Port 2 I/O Direction 1FD2 1111 1111

P5_DIR Port 5 I/O Direction 1FF3 1111 1111

P7_DIR (MD) Port 7 I/O Direction 1FD3 1111 1111

P1_MODE (MH) Port 1 Mode 1F99 0000 0000

P2_MODE Port 2 Mode 1FD0 0000 0000

P5_MODE Port 5 Mode 1FF1

††

P7_MODE (MD) Port 7 Mode 1FD1 0000 0000

P0_PIN (MC, MD)

P0_PIN (MH)

Port 0 Pin Input

1FA8

†

1FDA

P1_PIN (MC, MD)

P1_PIN (MH)

Port 1 Pin Input

1FA9

†

1F9F

P2_PIN Port 2 Pin Input 1FD6 †

P3_PIN Port 3 Pin Input 1FFE †

P4_PIN Port 4 Pin Input 1FFF †

P5_PIN Port 5 Pin Input 1FF7 1111 1111

Table C-2. Register Name, Address, and Reset Status (Continued)

Register

Mnemonic

Register Name

Hex

Addr

Binary Reset Value

High Low

†

Reset value is FFH when pin is not driven.

††

Reset value is 80H if the EA# pin is high, A9H if EA# is low.

†††

The CCRs are loaded with the contents of the chip configuration bytes (CCBs) after a device reset,

unless the device is entering programming modes (see “Entering Programming Modes” on page

16-13), in which case the programming chip configuration bytes (PCCBs) are used. The CCBs reside in

internal nonvolatile memory at addresses 2018H (CCB0) and 201AH (CCB1).