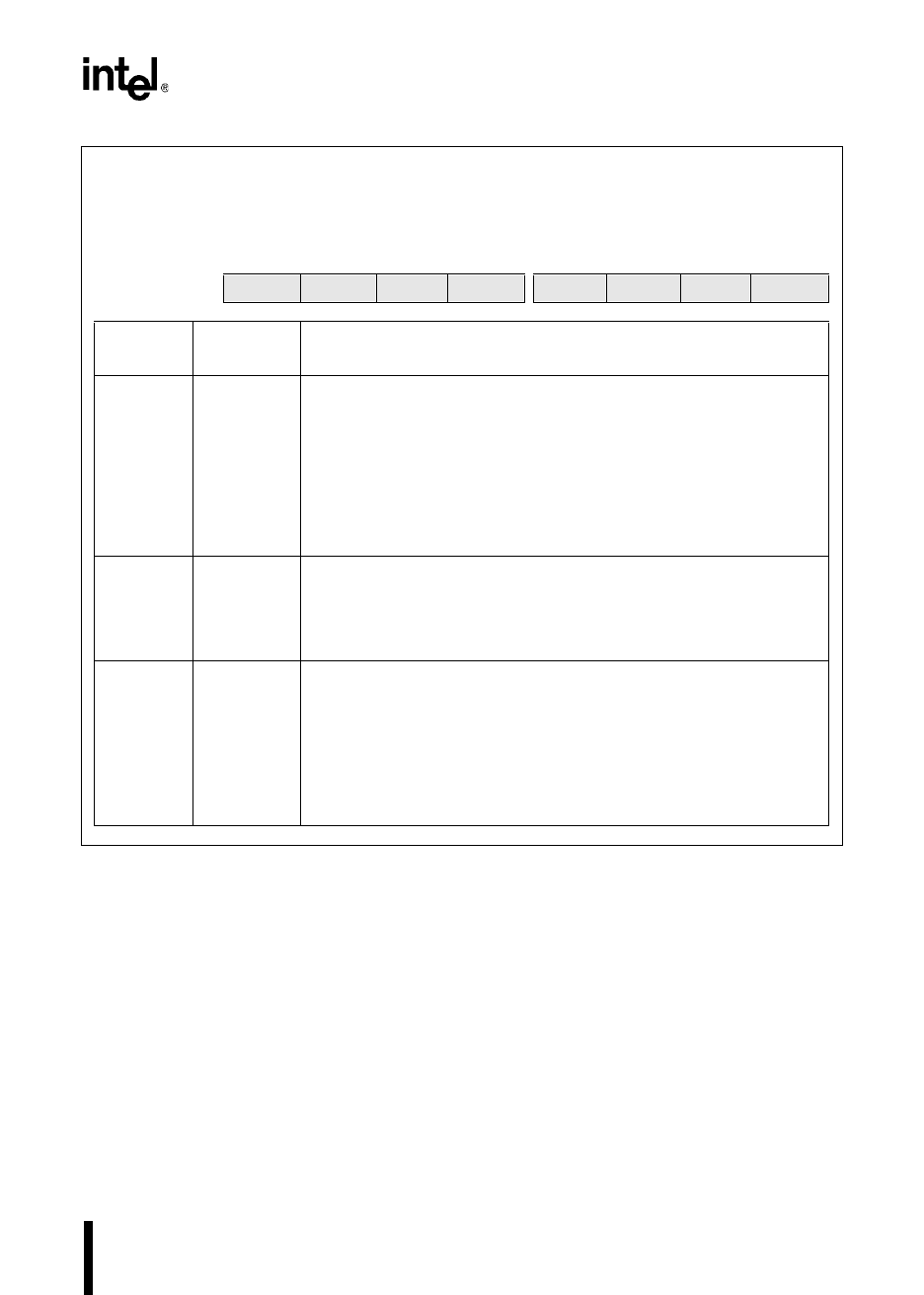

7-11

SERIAL I/O (SIO) PORT

3 REN Receive Enable

Setting this bit enables receptions. When this bit is set, a falling edge on

the RXD

x

pin starts a reception in mode 1, 2, or 3. In mode 0, this bit must

be clear for transmission to begin and must be set for reception to begin.

Clearing this bit stops a reception in progress and inhibits further

receptions. To avoid a partial or undesired reception, clear this bit before

clearing the RI flag in SP

x

_STATUS. This can be handled in an interrupt

environment by using software flags or in straight-line code by using the

interrupt pending register to signal the completion of a reception.

2 PEN Parity Enable

In modes 1 and 3, setting this bit enables the parity function. This bit must

be cleared if mode 2 is used. When this bit is set, TB8 takes the parity

value on transmissions and SP

x

_STATUS.7 becomes the receive parity

error bit.

1:0 M1:0 Mode Selection

These bits along with bit 7 select the communications mode.

M2 M1 M0

0 0 0 synchronous mode 0

X01 mode 1

X10 mode 2

X11 mode 3

1 0 0 synchronous mode 4

SP

x

_CON (Continued)

x

= 0–1 (8XC196MH)

Address:

Reset State:

1F83H, 1F8BH

00H

The serial port control (SP

x

_CON) register selects the communications mode and enables or disables

the receiver, parity checking, and nine-bit data transmission.

7 0

8XC196MH

M2 DIR PAR TB8 REN PEN M1 M0

Bit

Number

Bit

Mnemonic

Function

Figure 7-6. Serial Port Control (SP

x

_CON) Register (Continued)