15-1

CHAPTER 15

INTERFACING WITH EXTERNAL MEMORY

The microcontroller can interface with a variety of external memory devices. It supports either a

fixed 8-bit data bus width, a fixed 16-bit data bus width, or a dynamic 8-bit/16-bit data bus width;

internal control of wait states for slow external memory devices; and several bus-control modes.

These features provide a great deal of flexibility when interfacing with external memory systems.

In addition to describing the signals and registers related to external memory, this chapter discuss-

es the process of fetching the chip configuration bytes and configuring the external bus. It also

provides examples of external memory configurations.

15.1 EXTERNAL MEMORY INTERFACE SIGNALS AND REGISTERS

Table 15-1 lists the signals and Table 15-2 lists the registers that are mentioned in this chapter.

Many of the external memory interface signals are multiplexed with standard I/O port signals, as

shown in the Port Pin column. Table 15-3 gives the port register settings to configure the pins as

external memory interface signals rather than standard I/O port signals. See Chapter 6, “I/O

Ports,” to configure the pins as standard I/O port signals.

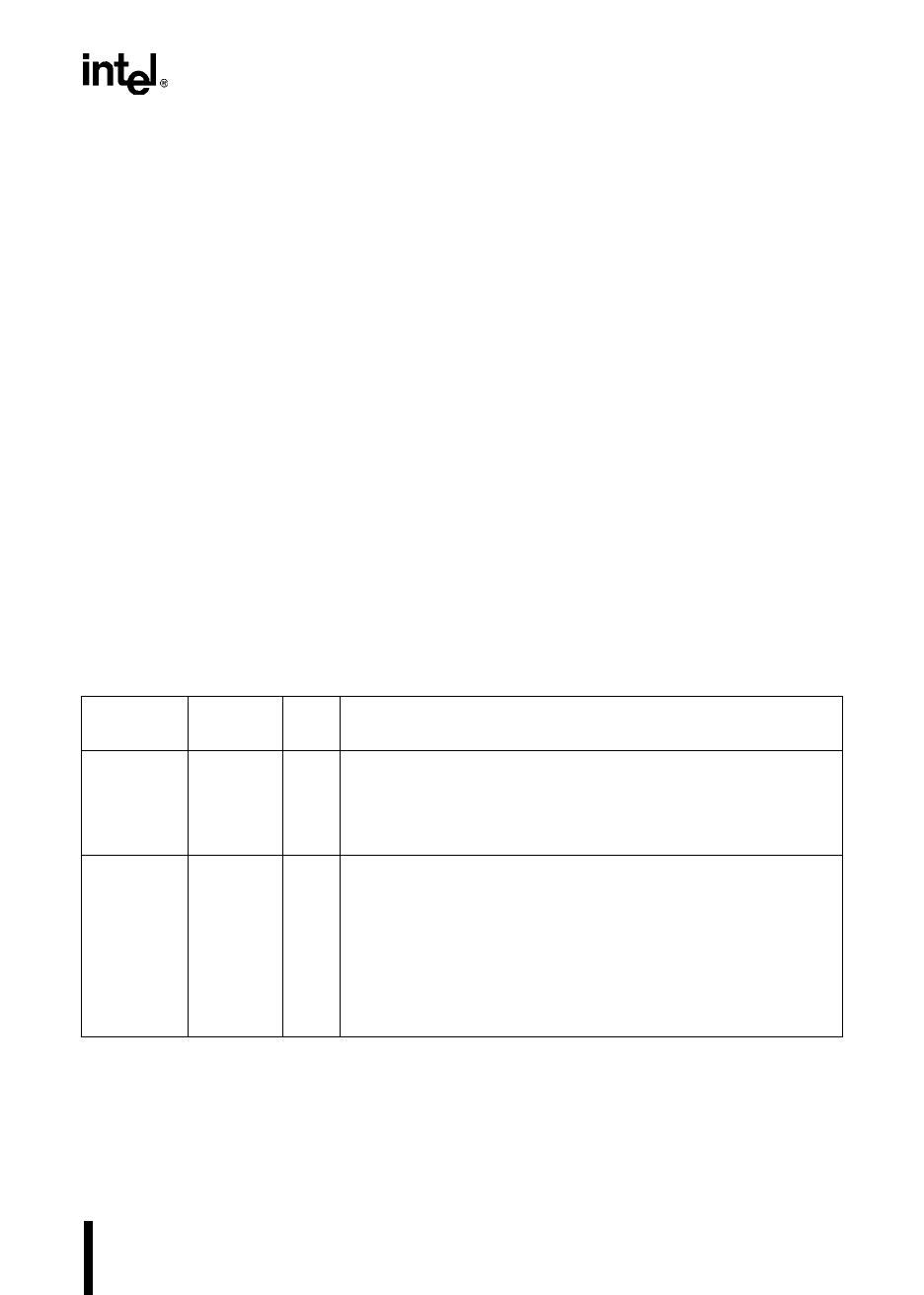

Table 15-1. External Memory Interface Signals

Signal

Name

Port Pin Type Description

AD15:0 P4.7:0

P3.7:0

I/O Address/Data Lines

These pins provide a multiplexed address and data bus. During the

address phase of the bus cycle, address bits 0–15 are presented on

the bus and can be latched using ALE or ADV#. During the data

phase, 8- or 16-bit data is transferred.

ADV# P5.0 O Address Valid

This active-low output signal is asserted only during external memory

accesses. ADV# indicates that valid address information is available

on the system address/data bus. The signal remains low while a valid

bus cycle is in progress and is returned high as soon as the bus cycle

completes.

An external latch can use this signal to demultiplex the address from

the address/data bus. A decoder can also use this signal to generate

chip selects for external memory.