8XC196MC, MD, MH USER’S MANUAL

15-22

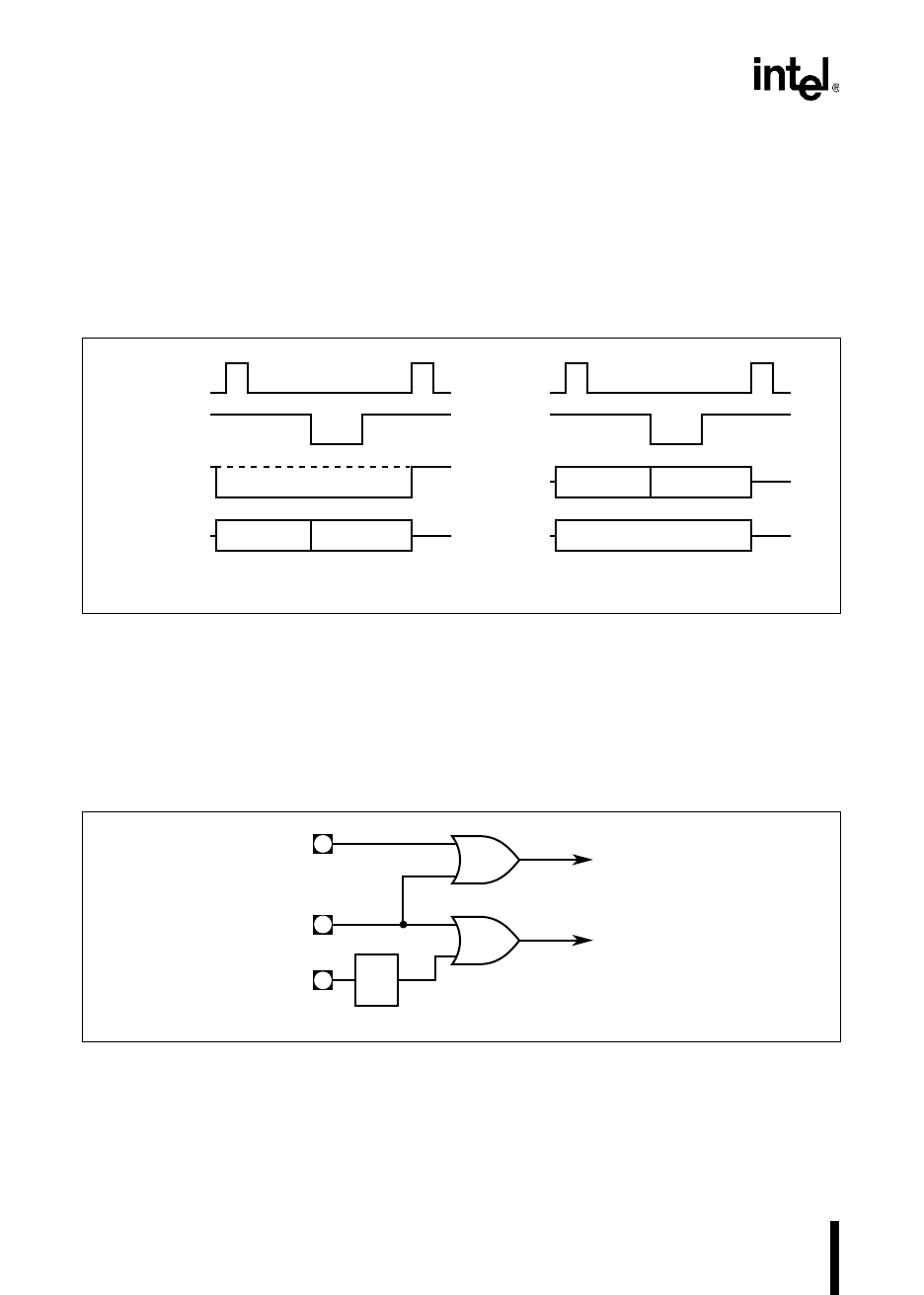

15.5.1 Standard Bus-control Mode

In the standard bus-control mode, the microcontroller generates the standard bus-control signals:

ALE, RD#, WR#, and BHE# (see Figure 15-10). ALE is asserted while the address is driven, and

it can be used to latch the address externally. RD# is asserted for every external memory read, and

WR# is asserted for every external memory write. When asserted, BHE# selects the bank of mem-

ory that is addressed by the high byte of the data bus.

Figure 15-10. Standard Bus Control

When the microcontroller is configured to use a 16-bit bus, separate low- and high-byte write sig-

nals must be generated for single-byte writes. Figure 15-11 shows a sample circuit that combines

BHE# and AD0 to produce these signals (WRL# and WRH#). A similar pair of signals for read

is unnecessary. For a single-byte read with the 16-bit bus, both bytes are placed on the data bus

and the processor discards the unwanted byte.

Figure 15-11. Decoding WRL# and WRH#

ALE

WR# or RD#

BHE#

AD15:0

Valid

Addr Data Out

16-bit Bus Cycle

ALE

WR# or RD#

AD7:0

AD15:8 Address High

Addr Low Data Out

8-bit Bus Cycle

A3077-01

BHE#

WR#

AD0

WRH#

WRL#

A3109-03

A0

74AC

373