8XC196MC, MD, MH USER’S MANUAL

C-40

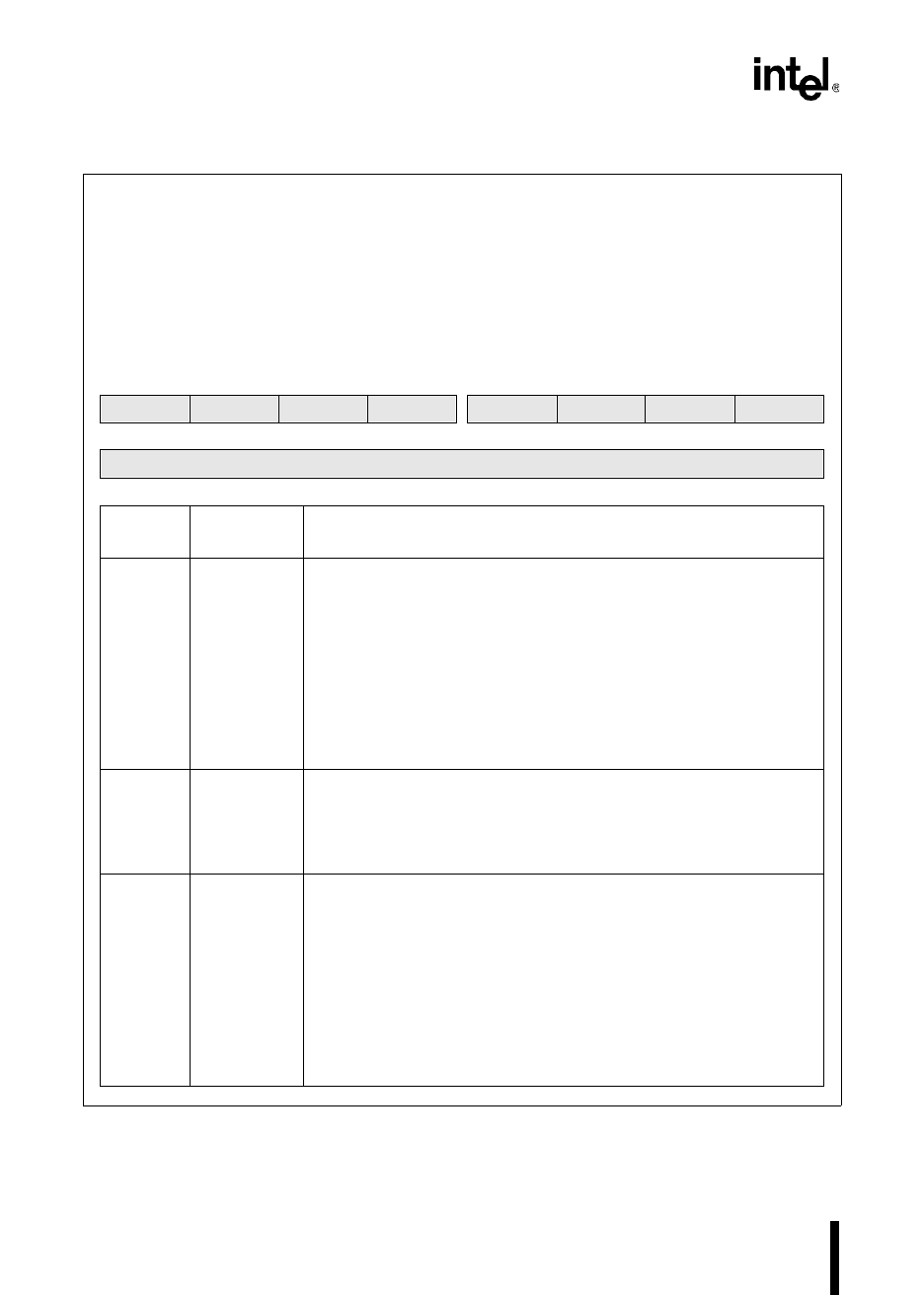

PSW

PSW

no direct access

The processor status word (PSW) actually consists of two bytes. The high byte is the status word,

which is described here; the low byte is the INT_MASK register. The status word contains one bit

(PSW.1) that globally enables or disables servicing of all maskable interrupts, one bit (PSW.2) that

enables or disables the peripheral transaction server (PTS), and six Boolean flags that reflect the

state of a user’s program.

The status word portion of the PSW cannot be accessed directly. To access the status word, push the

value onto the stack (PUSHF), then pop the value to a register (POP

test_reg

). The PUSHF and

PUSHA instructions save the PSW in the system stack and then clear it; POPF and POPA restore it.

15 8

Z N V VT C PSE I ST

7 0

See INT_MASK on page C-25

Bit

Number

Bit

Mnemonic

Function

15 Z Zero Flag

This flag is set to indicate that the result of an operation was zero. For

multiple-precision calculations, the zero flag cannot be set by the instruc-

tions that use the carry bit from the previous calculation (e.g., ADDC,

SUBC). However, these instructions can clear the zero flag. This

ensures that the zero flag will reflect the result of the entire operation, not

just the last calculation. For example, if the result of adding together the

lower words of two double words is zero, the zero flag would be set.

When the upper words are added together using the ADDC instruction,

the flag remains set if the result is zero and is cleared if the result is not

zero.

14 N Negative Flag

This flag is set to indicate that the result of an operation is negative. The

flag is correct even if an overflow occurs. For all shift operations and the

NORML instruction, the flag is set to equal the most-significant bit of the

result, even if the shift count is zero.

13 V Overflow Flag

This flag is set to indicate that the result of an operation is too large to be

represented correctly in the available space. For shift operations (SHL,

SHLB, and SHLL), the flag is set if the most-significant bit of the operand

changes during the shift. For divide operations, the quotient is stored in

the low-order half of the destination operand and the remainder is stored

in the high-order half. The overflow flag is set if the quotient is outside

the range for the low-order half of the destination operand. (Chapter 3,

“Programming Considerations,” defines the operands and possible

values for each. See the PSW flag descriptions in Appendix A for

details.)