8XC196MC, MD, MH USER’S MANUAL

5-28

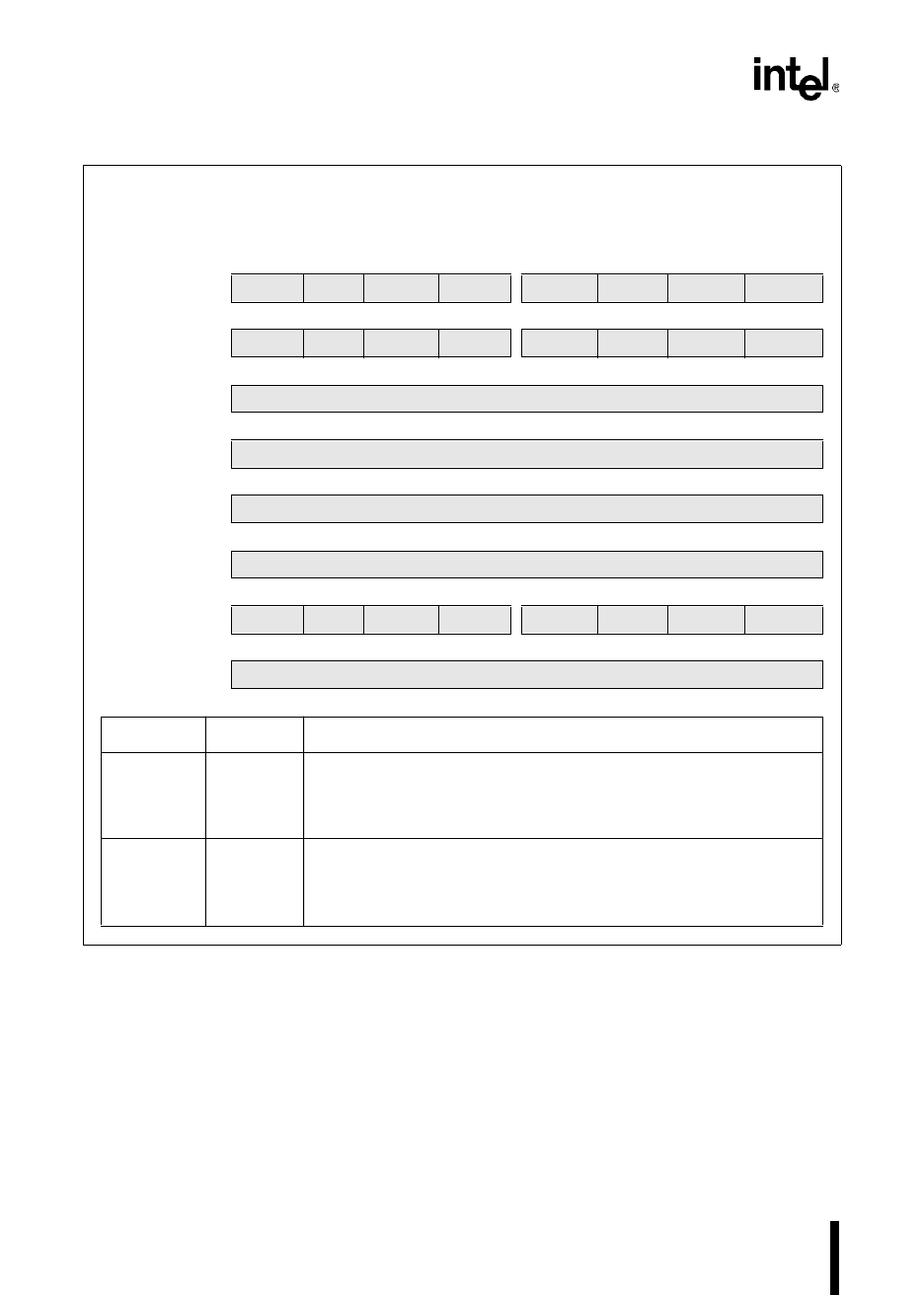

PTS Single Transfer Mode Control Block

In single transfer mode, the PTS control block contains a source and destination address (PTSSRC

and PTSDST), a control register (PTSCON), and a transfer count (PTSCOUNT).

7 0

Unused

0 0 0 0 0 0 0 0

7 0

Unused

0 0 0 0 0 0 0 0

15 8

PTSDST (H)

PTS Destination Address (high byte)

7 0

PTSDST (L)

PTS Destination Address (low byte)

15 8

PTSSRC (H)

PTS Source Address (high byte)

7 0

PTSSRC (L)

PTS Source Address (low byte)

7 0

PTSCON

M2 M1 M0 BW SU DU SI DI

7 0

PTSCOUNT

Consecutive Byte or Word Transfers

Register Location Function

PTSDST PTSCB + 4 PTS Destination Address

Write the destination memory location to this register. A valid address is

any unreserved memory location; however, it must point to an even

address if word transfers are selected.

PTSSRC PTSCB + 2 PTS Source Address

Write the source memory location to this register. A valid address is any

unreserved memory location; however, it must point to an even address

if word transfers are selected.

Figure 5-16. PTS Control Block — Single Transfer Mode