8XC196MC, MD, MH USER’S MANUAL

4-10

4.1.6.1 General-purpose Register RAM

The lower register file contains general-purpose register RAM. The stack pointer locations can

also be used as general-purpose register RAM when stack operations are not being performed.

The RALU can access this memory directly, using register-direct addressing.

The upper register file also contains general-purpose register RAM. The RALU normally uses

indirect or indexed addressing to access the RAM in the upper register file. Windowing enables

the RALU to use register-direct addressing to access this memory. (See Chapter 3, “Programming

Considerations,” for a discussion of addressing modes.) Windowing can provide for fast context

switching of interrupt tasks and faster program execution. (See “Windowing” on page 4-12.) PTS

control blocks and the stack are most efficient when located in the upper register file.

4.1.6.2 Stack Pointer (SP)

Memory locations 0018H and 0019H contain the stack pointer (SP). The SP contains the address

of the stack. The SP must point to a word (even) address that is two bytes greater than the desired

starting address. Before the CPU executes a subroutine call or interrupt service routine, it decre-

ments the SP by two and copies (PUSHes) the address of the next instruction from the program

counter onto the stack. It then loads the address of the subroutine or interrupt service routine into

the program counter. When it executes the return-from-subroutine (RET) instruction at the end of

the subroutine or interrupt service routine, the CPU loads (POPs) the contents of the top of the

stack (that is, the return address) into the program counter and increments the SP by two.

Subroutines may be nested. That is, each subroutine may call other subroutines. The CPU pushes

the contents of the program counter onto the stack each time it executes a subroutine call. The

stack grows downward as entries are added. The only limit to the nesting depth is the amount of

available memory. As the CPU returns from each nested subroutine, it pops the address off the

top of the stack, and the next return address moves to the top of the stack.

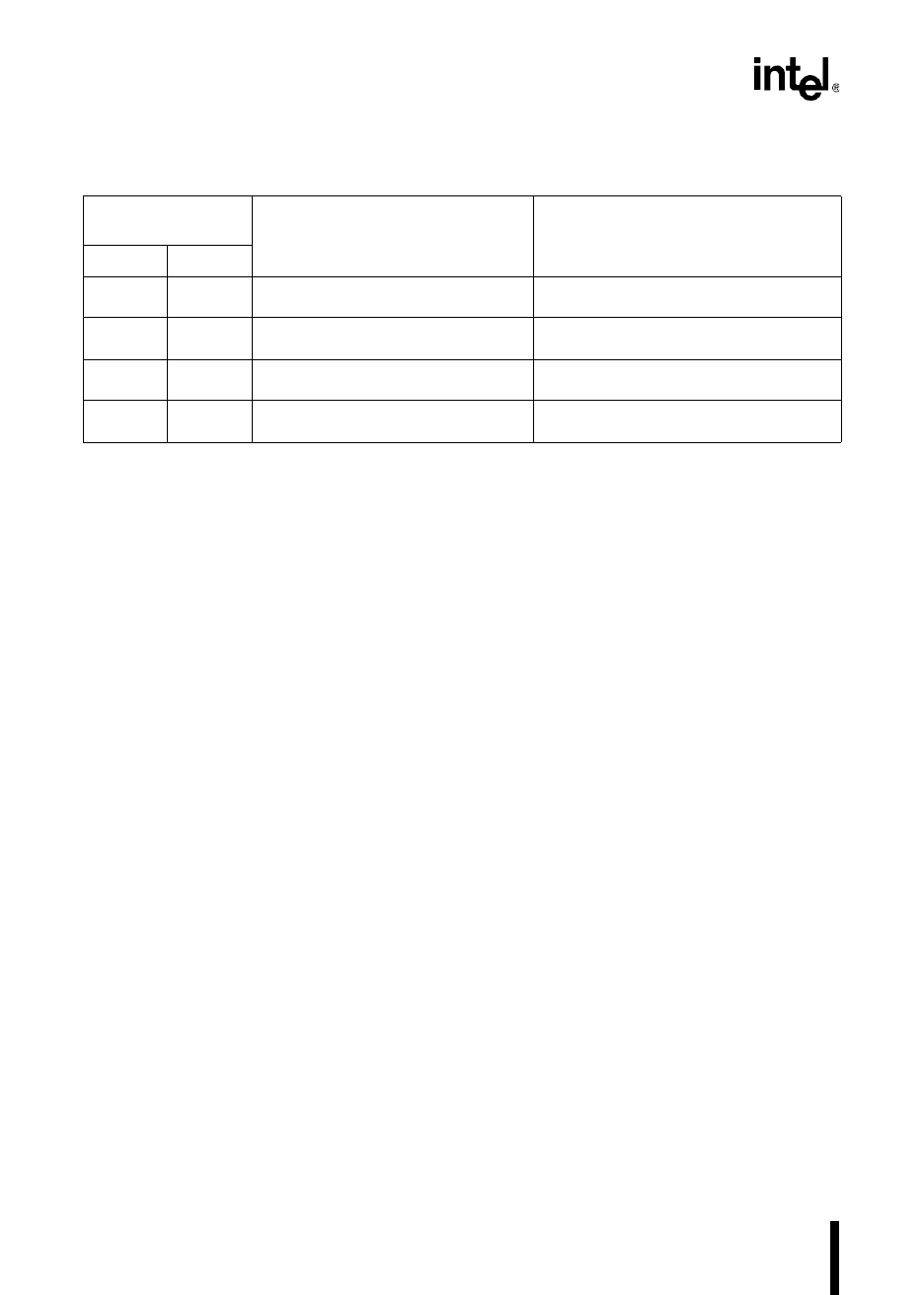

Table 4-7. Register File Memory Addresses

Device and Hex

Address Range

Description Addressing Modes

MC, MD MH

01FF

0100

02FF

0100

Upper register file (register RAM) Indirect, indexed, or windowed direct

00FF

001A

00FF

001A

Lower register file (register RAM) Direct, indirect, or indexed

0019

0018

0019

0018

Lower register file (stack pointer) Direct, indirect, or indexed

0017

0000

0017

0000

Lower register file (CPU SFRs) Direct, indirect, or indexed