8XC196MC, MD, MH USER’S MANUAL

A-36

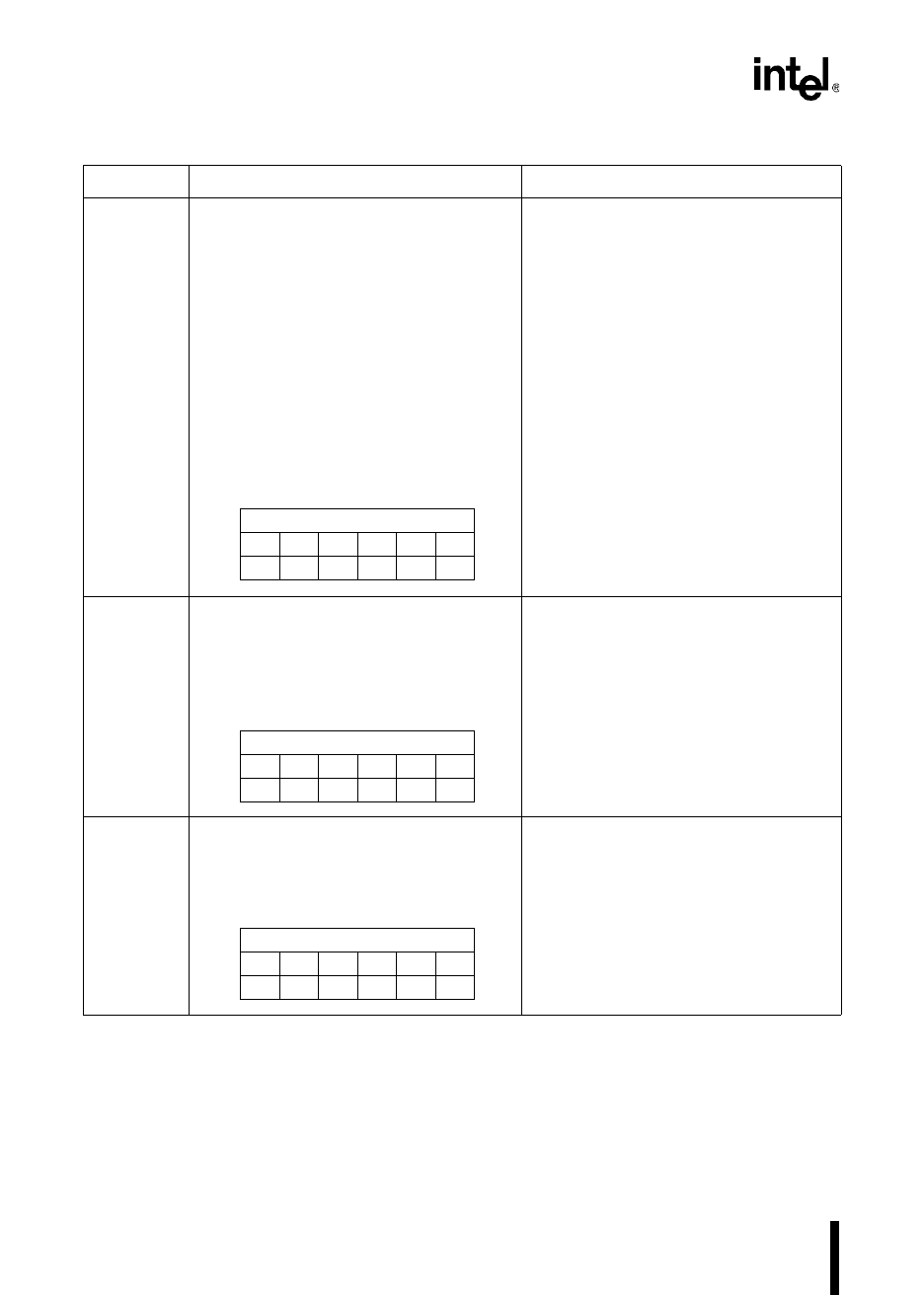

SHRL LOGICAL RIGHT SHIFT DOUBLE-WORD.

Shifts the destination double-word operand to

the right as many times as specified by the

count operand. The count may be specified

either as an immediate value in the range of 0

to 15 (0FH), inclusive, or as the content of

any register (10H – 0FFH) with a value in the

range of 0 to 31 (1FH), inclusive. The left bits

of the result are filled with zeros. The last bit

shifted out is saved in the carry flag.

Te mp

← (COUNT)

do while Temp

≠ 0

C

← Low order bit of (DEST)

(DEST)

← (DEST)/2)

Te mp

← Temp – 1

end_while

SHRL lreg, #count

(00001100) (count) (lreg)

or

SHRL lreg, breg

(00001100) (breg) (lreg)

NOTES: This instruction clears the

sticky bit flag at the beginning

of the instruction. If at any time

during the shift a “1” is shifted

into the carry flag and another

shift cycle occurs, the instruc-

tion sets the sticky bit flag.

In this operation, (DEST)/2 rep-

resents unsigned division.

PSW Flag Settings

ZNCVVTST

✓0✓0—✓

SJMP SHORT JUMP. Adds to the program counter

the offset between the end of this instruction

and the target label, effecting the jump. The

offset must be in the range of –1024 to

+1023, inclusive.

PC

← PC + 11-bit disp

SJMP cadd

(00100xxx) (disp-low)

NOTE: The displacement (disp) is sign-

extended to 16 bits.

PSW Flag Settings

ZNCVVTST

——————

SKIP TWO BYTE NO-OPERATION. Does nothing.

Control passes to the next sequential

instruction. This is actually a two-byte NOP in

which the second byte can be any value and

is simply ignored.

SKIP breg

(00000000) (breg)

PSW Flag Settings

ZNCVVTST

——————

Table A-6. Instruction Set (Continued)

Mnemonic Operation Instruction Format