8XC196MC, MD, MH USER’S MANUAL

C-68

WSR

WSR

Address:

Reset State:

0014H

00H

The window selection register (WSR) maps sections of RAM into the top of the lower register file, in

32-, 64-, or 128-byte increments. PUSHA saves this register on the stack and POPA restores it.

7 0

— W6 W5 W4 W3 W2 W1 W0

Bit

Number

Bit

Mnemonic

Function

7 — Reserved; for compatibility with future devices, write zero to this bit.

6:0 W6:0 Window Selection

These bits specify the window size and number. Table C-12 shows the WSR

settings and direct addresses for windowable SFRs.

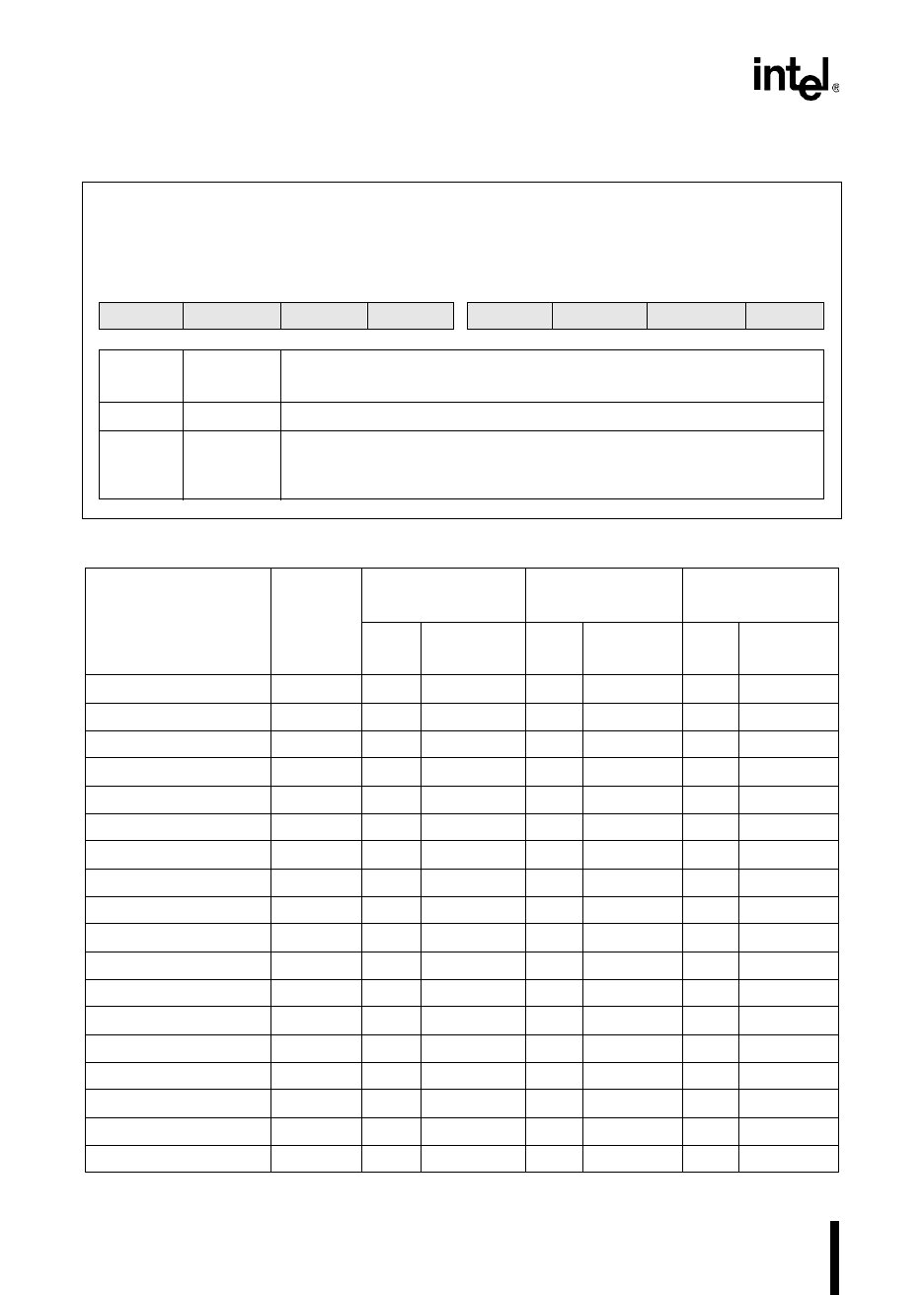

Table C-12. WSR Settings and Direct Addresses for Windowable SFRs

Register Mnemonic

Memory

Location

32-byte Windows

(00E0–00FFH)

64-byte Windows

(00C0–00FFH)

128-byte Windows

(0080–00FFH)

WSR

Direct

Address

WSR

Direct

Address

WSR

Direct

Address

AD_COMMAND 1FACH 7DH 00ECH 3EH 00ECH 1FH 00ACH

AD_RESULT 1FAAH 7DH 00EAH 3EH 00EAH 1FH 00AAH

AD_TEST 1FAEH 7DH 00EEH 3EH 00EEH 1FH 00AEH

AD_TIME 1FAFH 7DH 00EFH 3EH 00EFH 1FH 00AFH

COMP0_CON 1F58H 7AH 00F8H 3DH 00D8H 1EH 00D8H

COMP1_CON 1F5CH 7AH 00FCH 3DH 00DCH 1EH 00DCH

COMP2_CON 1F60H 7BH 00E0H 3DH 00E0H 1EH 00E0H

COMP3_CON 1F64H 7BH 00E4H 3DH 00E4H 1EH 00E4H

COMP4_CON (MD) 1F68H 7BH 00E8H 3DH 00E8H 1EH 00E8H

COMP5_CON (MD) 1F6CH 7BH 00ECH 3DH 00ECH 1EH 00ECH

COMP0_TIME

†

1F5AH 7AH 00FAH 3DH 00DAH 1EH 00DAH

COMP1_TIME

†

1F5EH 7AH 00FEH 3DH 00DEH 1EH 00DEH

COMP2_TIME

†

1F62H 7BH 00E2H 3DH 00E2H 1EH 00E2H

COMP3_TIME

†

1F66H 7BH 00E6H 3DH 00E6H 1EH 00E6H

COMP4_TIME

†

(MD) 1F6AH 7BH 00EAH 3DH 00EAH 1EH 00EAH

COMP5_TIME

†

(MD) 1F6EH 7BH 00EEH 3DH 00EEH 1EH 00EEH

EPA0_CON 1F40H 7AH 00E0H 3DH 00C0H 1EH 00C0H

EPA1_CON

†

1F44H 7AH 00E4H 3DH 00C4H 1EH 00C4H

†

Must be addressed as a word.