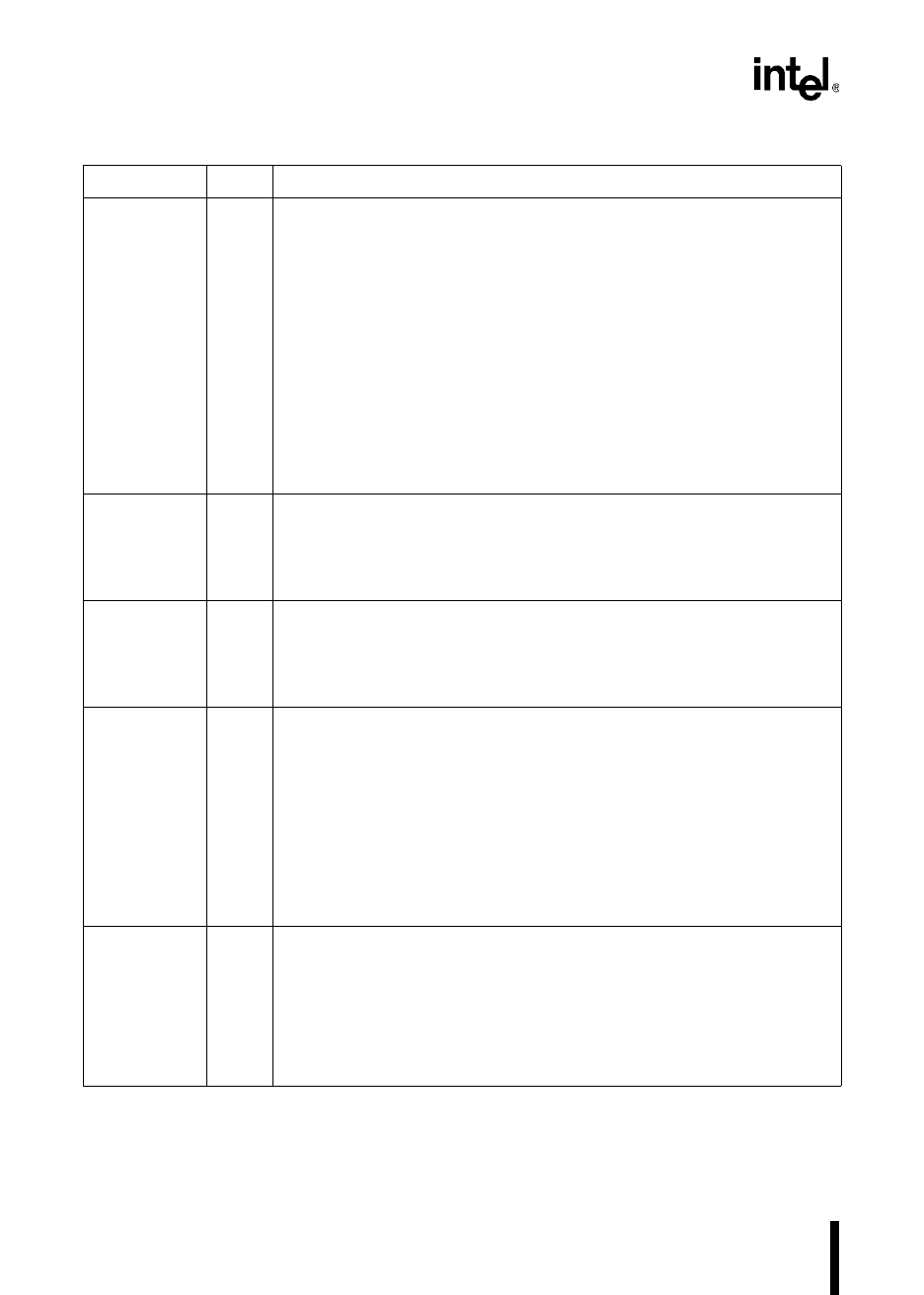

8XC196MC, MD, MH USER’S MANUAL

B-18

P2.7:0 I/O Port 2

This is a standard, 8-bit, bidirectional port that is multiplexed with individually

selectable special-function signals.

P2.6 is multiplexed with a special test-mode-entry function. If this pin is held low

during reset, the device will enter a reserved test mode, so exercise caution if

you use this pin for input. If you choose to configure this pin as an input, always

hold it high during reset and ensure that your system meets the V

IH

specification

(see datasheet) to prevent inadvertent entry into ONCE mode.

On the 8XC196MC and MD, port 2 is multiplexed as follows: P2.0/EPA0/PVER,

P2.1/EPA1/PALE#, P2.2/EPA2/PROG#, P2.3/EPA3, P2.4/COMP0/AINC#,

P2.5/COMP1/PACT#, P2.6/COMP2/CPVER, and P2.7/COMP3.

On the 8XC196MH, port 2 is multiplexed as follows: P2.0/EPA0/PVER,

P2.1/SCLK0#/BCLK0/PALE#, P2.2/EPA1/PROG#, P2.3/COMP3,

P2.4/COMP0/AINC#, P2.5/COMP1/PACT#, P2.6/COMP2/CPVER, and

P2.7/SCLK1#/BCLK1.

P3.7:0 I/O Port 3

This is a memory-mapped, 8-bit, bidirectional port with programmable open-

drain or complementary output modes. The pins are shared with the

multiplexed address/data bus, which has complementary drivers.

P3.7:0 are multiplexed with AD7:0 and PBUS.7:0.

P4.7:0 I/O Port 4

This is a memory-mapped, 8-bit, bidirectional port with programmable open-

drain or complementary output modes. The pins are shared with the

multiplexed address/data bus, which has complementary drivers.

P4.7:0 are multiplexed with AD15:8 and PBUS15:8.

P5.7:0 I/O Port 5

This is a memory-mapped, 8-bit, bidirectional port that is multiplexed with

individually selectable control signals.

P5.4 is multiplexed with the ONCE# function. If this pin is held low during reset,

the device will enter ONCE mode , so exercise caution if you use this pin for

input. If you choose to configure this pin as an input, always hold it high during

reset and ensure that your system meets the V

IH

specification (see datasheet)

to prevent inadvertent entry into ONCE mode.

Port 5 is multiplexed as follows: P5.0/ALE/ADV#, P5.1/INST, P5.2/WR#/WRL#,

P5.3/RD#, P5.4/ONCE#, P5.5/BHE#/WRH#, P5.6/READY, and

P5.7/BUSWIDTH.

P6.7:0 O Port 6

This is a standard, 8-bit, output-only port that is multiplexed with the special

functions of the waveform generator and PWM peripherals. The WG_OUT

register configures the pins, establishes the output polarity, and controls

whether changes to the outputs are synchronized with an event or take effect

immediately.

Port 6 is multiplexed as follows: P6.0/WG1#, P6.1/WG1, P6.2/WG2#,

P6.3/WG2, P6.4/WG3#, P6.5/WG3, P6.6/PWM0, and P6.7/PWM1.

Table B-6. Signal Descriptions (Continued)

Name Type Description