8XC196MC, MD, MH USER’S MANUAL

C-4

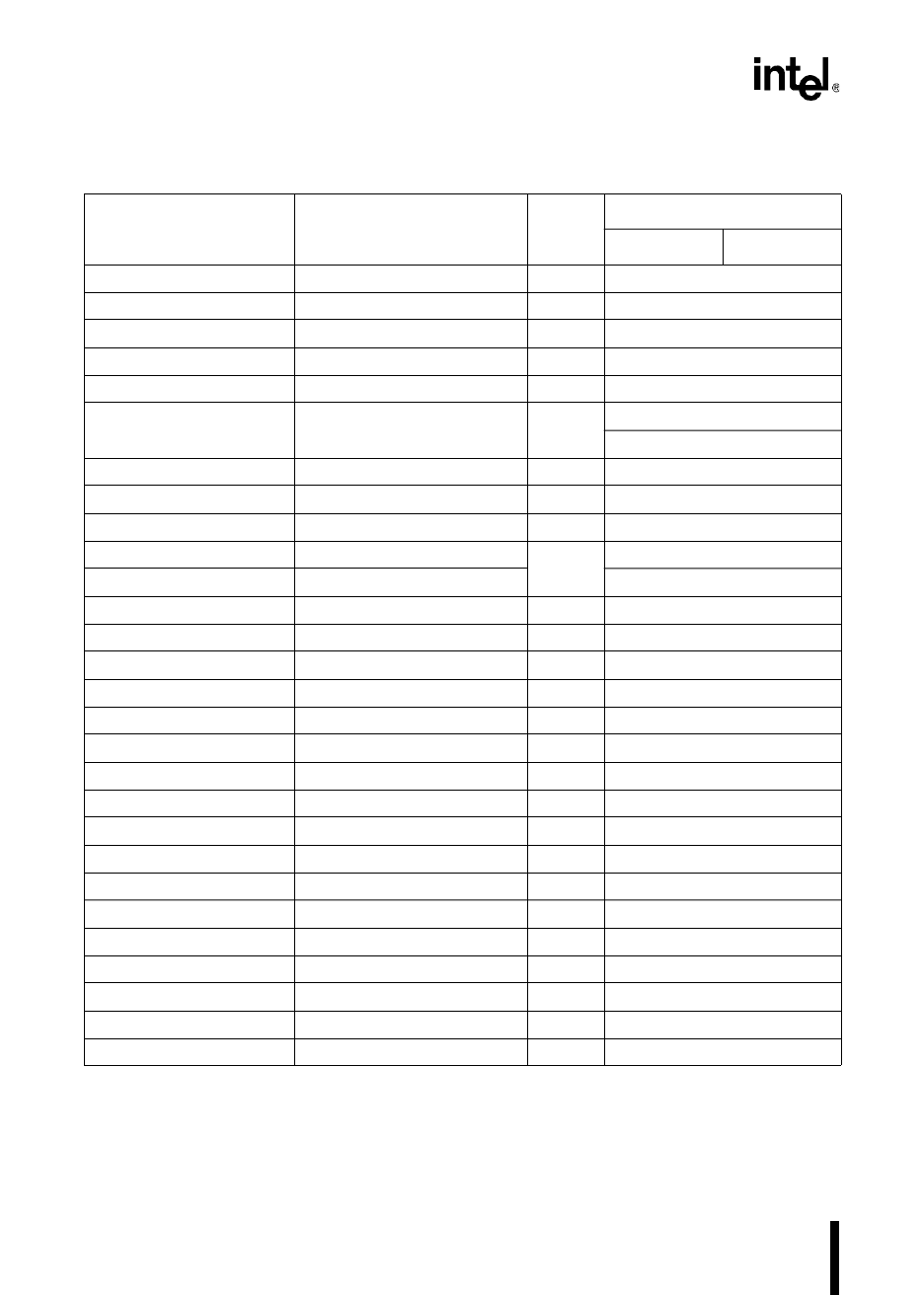

P7_PIN (MD) Port 7 Pin Input 1FD7 XXXX XXXX

P1_REG (MH) Port 1 Data Output 1F9D 1111 1111

P2_REG Port 2 Data Output 1FD4 1111 1111

P3_REG Port 3 Data Output 1FFC 1111 1111

P4_REG Port 4 Data Output 1FFD 1111 1111

P5_REG (MC, MD)

P5_REG (MH)

Port 5 Data Output 1FF5

†

1111 1111

P7_REG (MD) Port 7 Data Output 1FD5 1111 1111

PI_MASK Peripheral Interrupt Mask 1FBC 1010 1010

PI_PEND Peripheral Interrupt Pending 1FBE 1010 1010

PPW Programming Pulse Width

no direct

access

PSW Processor Status Word

PTSSEL PTS Select 0004 0000 0000 0000 0000

PTSSRV PTS Service 0006 0000 0000 0000 0000

PWM_COUNT PWM Count 1FB6 0000 0000

PWM_PERIOD PWM Period 1FB4 0000 0000

PWM0_CONTROL PWM 0 Control 1FB0 0000 0000

PWM1_CONTROL PWM 1 Control 1FB2 0000 0000

SBUF0_RX (MH) Serial Port Receive Buffer 1F80 0000 0000

SBUF1_RX (MH) Serial Port Receive Buffer 1F88 0000 0000

SBUF0_TX (MH) Serial Port Transmit Buffer 1F82 0000 0000

SBUF1_TX (MH) Serial Port Transmit Buffer 1F8A 0000 0000

SP Stack Pointer 0018 XXXX XXXX XXXX XXXX

SP0_BAUD (MH) Serial Port 0 Baud Rate 1F84 0000 0000 0000 0000

SP1_BAUD (MH) Serial Port 1 Baud Rate 1F8C 0000 0000 0000 0000

SP0_CON (MH) Serial Port Control 1F83 0000 0000

SP1_CON (MH) Serial Port Control 1F8B 0000 0000

SP0_STATUS (MH) Serial Port Status 1F81 0000 0000

SP1_STATUS (MH) Serial Port Status 1F89 0000 0000

Table C-2. Register Name, Address, and Reset Status (Continued)

Register

Mnemonic

Register Name

Hex

Addr

Binary Reset Value

High Low

†

Reset value is FFH when pin is not driven.

††

Reset value is 80H if the EA# pin is high, A9H if EA# is low.

†††

The CCRs are loaded with the contents of the chip configuration bytes (CCBs) after a device reset,

unless the device is entering programming modes (see “Entering Programming Modes” on page

16-13), in which case the programming chip configuration bytes (PCCBs) are used. The CCBs reside in

internal nonvolatile memory at addresses 2018H (CCB0) and 201AH (CCB1).