8XC196MC, MD, MH USER’S MANUAL

7-4

7.3 SERIAL PORT MODES

The serial port has both synchronous and asynchronous operating modes for transmission and re-

ception. This section describes the operation of each mode.

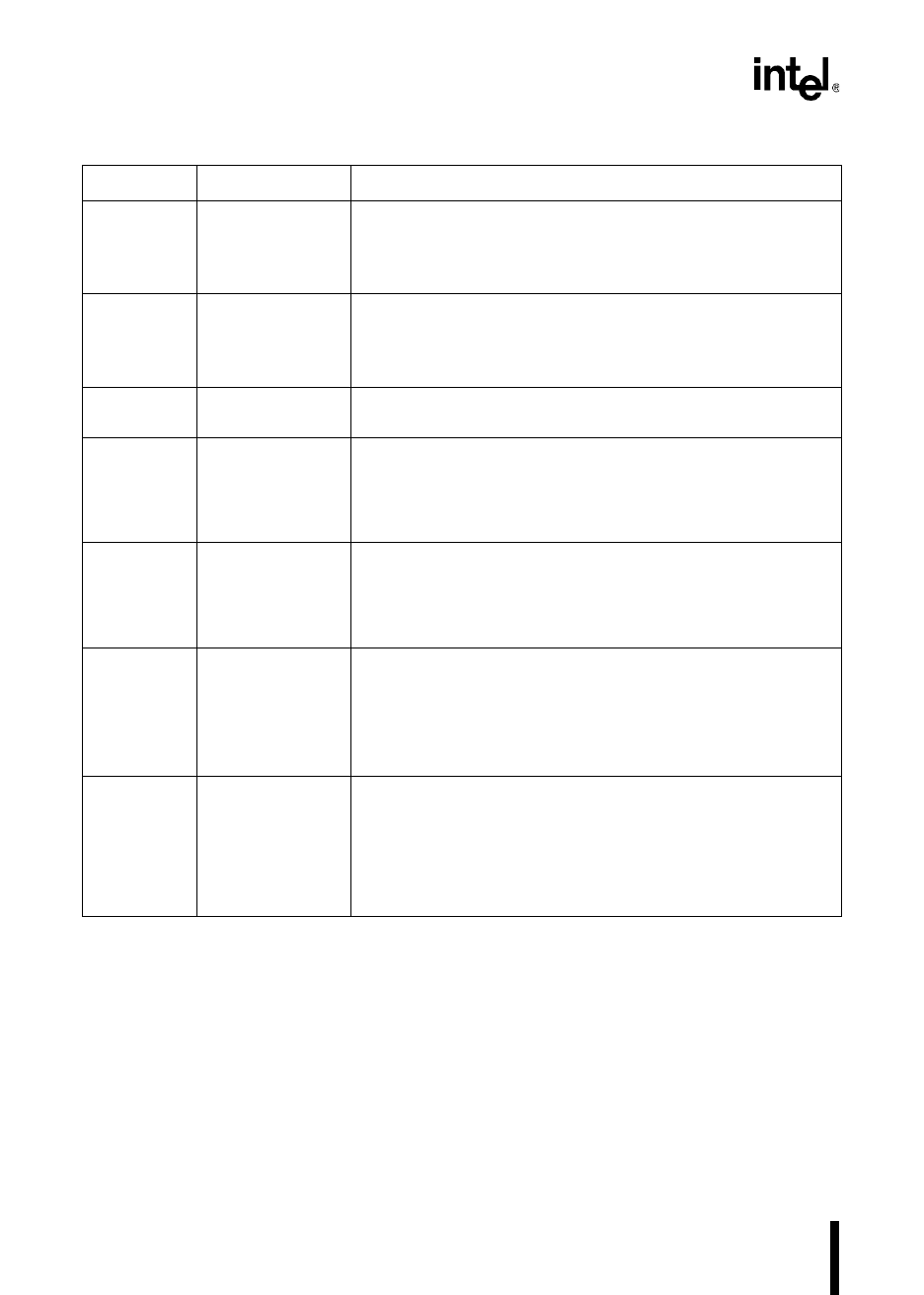

PI_MASK 1FBCH Peripheral Interrupt Mask

This register enables and disables multiplexed peripheral interrupts.

Setting an SP

x

bit enables a serial port receive error interrupt;

clearing the bit disables (masks) the interrupt.

PI_PEND 1FBEH Peripheral Interrupt Pending

This register indicates pending multiplexed peripheral interrupts.

When set, an SP

x

bit indicates a pending serial port receive error

interrupt.

SBUF0_RX

SBUF1_RX

1F80H

1F88H

Serial Port

x

Receive Buffer

This register contains data received from the serial port.

SBUF0_TX

SBUF1_TX

1F82H

1F8AH

Serial Port

x

Transmit Buffer

This register contains data that is ready for transmission. In modes

1, 2, and 3, writing to SBUF

x

_TX starts a transmission. In mode 0,

writing to SBUF

x

_TX starts a transmission only if the receiver is

disabled (SP

x

_CON.3 = 0).

SP0_BAUD

SP1_BAUD

1F84H,1F85H

1F8CH,1F8DH

Serial Port

x

Baud Rate

This register selects the serial port baud rate and clock source. The

most-significant bit selects the clock source. The lower 15 bits

represent the BAUD_VALUE, an unsigned integer that determines

the baud rate.

SP0_CON

SP1_CON

1F83H

1F8BH

Serial Port

x

Control

This register selects the communications mode and enables or

disables the receiver, parity checking, and ninth-bit data transmis-

sions. The TB8 bit is cleared after each transmission.

For mode 4, this register also selects the direction (input or output)

of the SCLKx# signal.

SP0_STATUS

SP1_STATUS

1F81H

1F89H

Serial Port

x

Status

This register contains the serial port status bits. It has status bits for

receive overrun errors (OE), transmit buffer empty (TXE), framing

errors (FE), transmit interrupt (TI), receive interrupt (RI), and

received parity error (RPE) or received bit 8 (RB8). Reading

SP

x

_STATUS clears all bits except TXE; writing a byte to

SBUF

x

_TX clears the TXE bit.

Table 7-2. Serial Port Control and Status Registers (Continued)

Mnemonic Address Description