Chip Select Unit

5-12

5.5.5 Peripheral Chip Select Register (PACS, Offset A4h)

Unlike the UCS and LCS chip selects, the PCS outputs assert with the same timing as the

multiplexed AD address bus. Also, each peripheral chip select asserts over a 256-byte

address range, which is twice the address range covered by peripheral chip selects in the

80C186 and 80C188 microcontrollers.

The Am186ER and Am188ER microcontrollers provide six chip selects, PCS

6–PCS5 and

PCS

3–PCS0, for use within a user-locatable memory or I/O block. (PCS4 is not

implemented on the Am186ER and Am 188ER microcontrollers.) The base address of the

memory block can be located anywhere within the 1-Mbyte memory address space,

exclusive of the areas associated with the UCS

, LCS, and MCS chip selects, or they can

be configured to access the 64-Kbyte I/O space.

The Peripheral Chip Selects are programmed through two registers—the Peripheral Chip

Select (PACS) Register and the PCS

and MCS Auxiliary (MPCS) Register. The Peripheral

Chip Select (PACS) Register (Figure 5-5) determines the base address, the ready condition,

and the wait states for the PCS

3–PCS0 outputs.

The PCS

and MCS Auxiliary (MPCS) Register (see Figure 5-4) contains bits that configure

the PCS

6–PCS5 pins as either chip selects or address pins A1 and A2. When the PCS6–

PCS

5 pins are chip selects, the MPCS Register also determines whether PCS chip selects

are active during memory or I/O bus cycles and specifies the ready and wait states for the

PCS

6–PCS5 outputs.

The PCS

pins are not active on reset. The PCS pins are activated as chip selects by writing

to both the PACS and MPCS registers.

PCS

6–PCS5 can be configured and activated as address pins by writing only the MPCS

Register. No corresponding access to the PACS Register is required in this case.

PCS

3–PCS0 can be configured for zero wait states to 15 wait states. PCS6–PCS5 can be

configured for zero wait states to three wait states.

Note: The PCS3–PCS0 and PCS6–PCS5 pins are multiplexed with programmable I/O

pins. To enable the PCS

3–PCS0 and PCS6–PCS5 pins to function as chip selects, the PIO

mode and PIO direction settings for the PCS

3–PCS0 and PCS6–PCS5 pins must be set

to 0 for normal operation. For more information, see Chapter 13, “Programmable I/O Pins.”

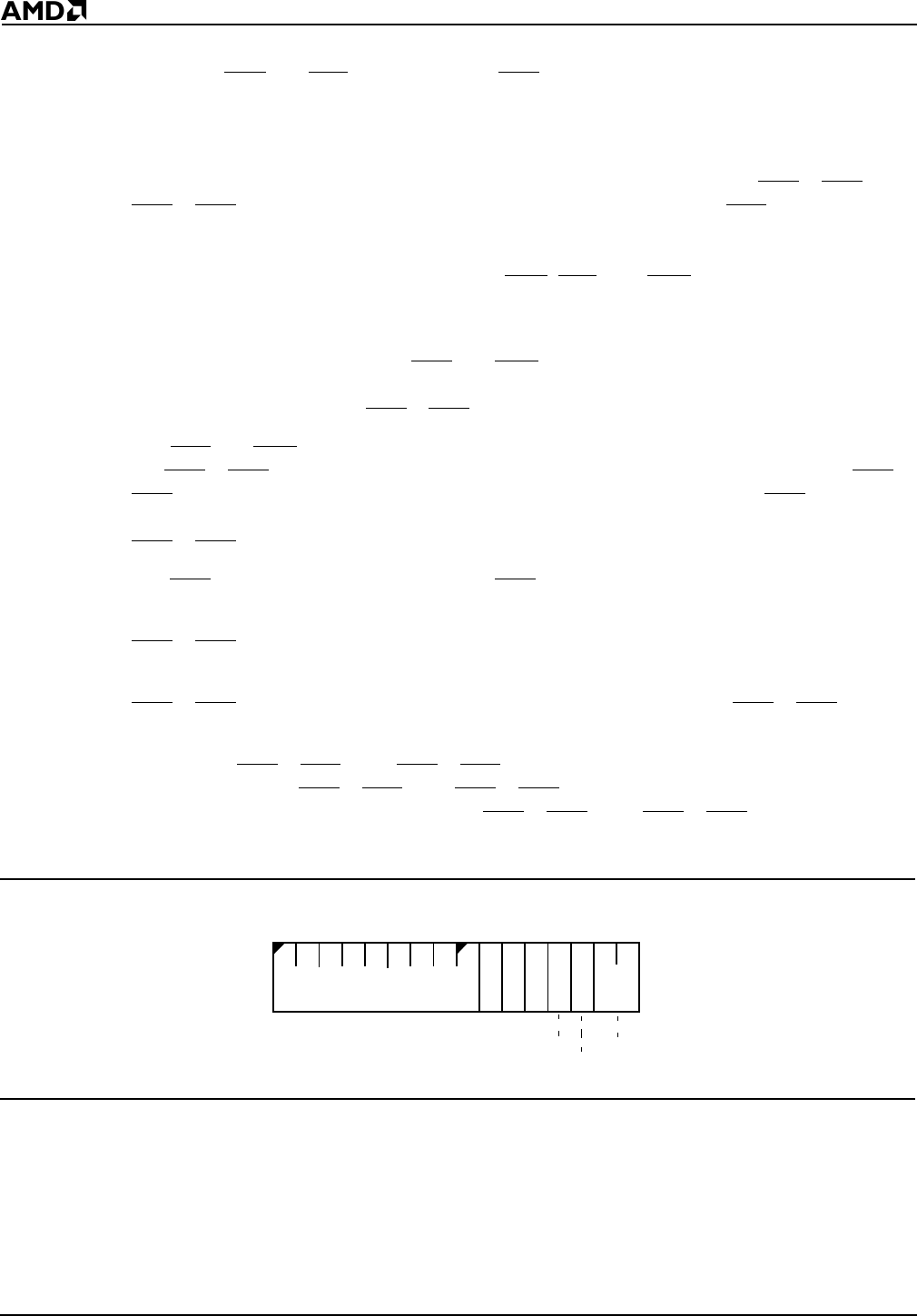

Figure 5-5 Peripheral Chip Select Register (PACS, offset A4h)

The value of the PACS Register at reset is undefined.

Bits 15–7: Base Address (BA19–BA11)—The base address of the peripheral chip select

block is defined by BA19–BA11 of the PACS Register. BA19–BA11 correspond to bits

19–11 of the 20-bit programmable base address of the peripheral chip select block. Bit 6

of the PACS Register corresponds to bit 10 of the base address in the 80C186 and 80C188

microcontrollers, and is not implemented. Thus, code previously written for the 80C186

15

70

BA19–BA11 1 11

R1–R0

R2

R3