Interrupt Control Unit

8-20

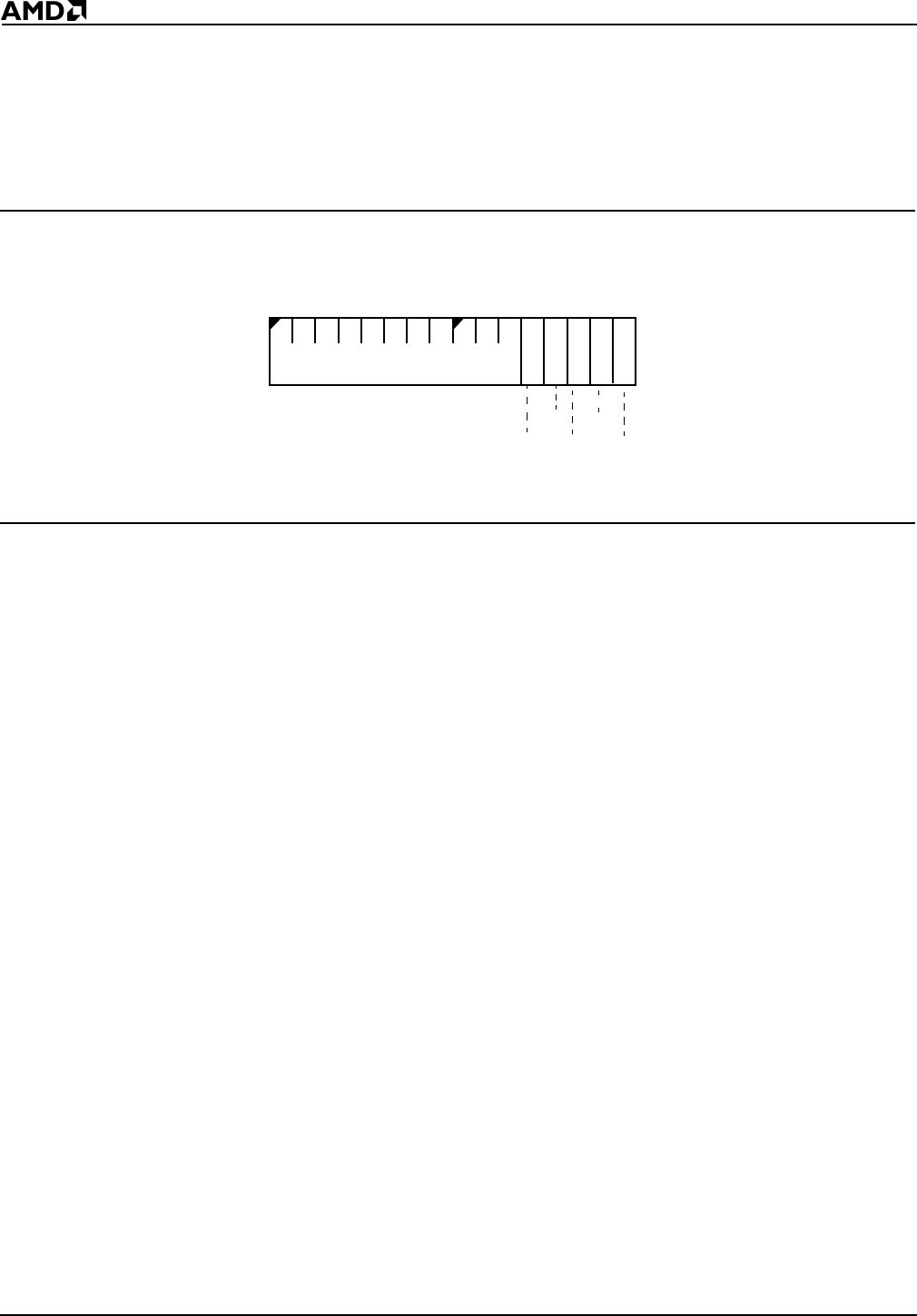

8.3.6 Serial Port Interrupt Control Register (SPICON, Offset 44h)

(Master Mode)

The Serial Port Interrupt Control (SPICON) Register controls the operation of the

asynchronous serial port interrupt source (SPI, bit 10 in the Interrupt Request Register).

This interrupt is assigned to interrupt type 14h. The control register format is shown in

Figure 8-9.

Figure 8-9 Serial Port Interrupt Control Register (SPICON, offset 44h)

The value of SPICON at reset is 001Fh.

Bits 15–5: Reserved—Set to 0.

Bit 4: Reserved—Set to 1.

Bit 3: Mask (MSK)—This bit determines whether the serial port can cause an interrupt. A

1 in this bit masks this interrupt source, preventing the serial port from causing an interrupt.

A 0 in this bit enables serial port interrupts.

This bit is duplicated in the Interrupt Mask Register. See the Interrupt Mask Register in

section 8.3.11 on page 8-25.

Bits 2–0: Priority (PR2–PR0)—This field determines the priority of the serial port relative to

the other interrupt signals. After a reset, the priority is 7. See Table 8-3, “Priority Level,” on

page 8-15.

15

70

MSK

Res

Reserved

1

PR2

PR1

PR0