DMA Controller

10-3

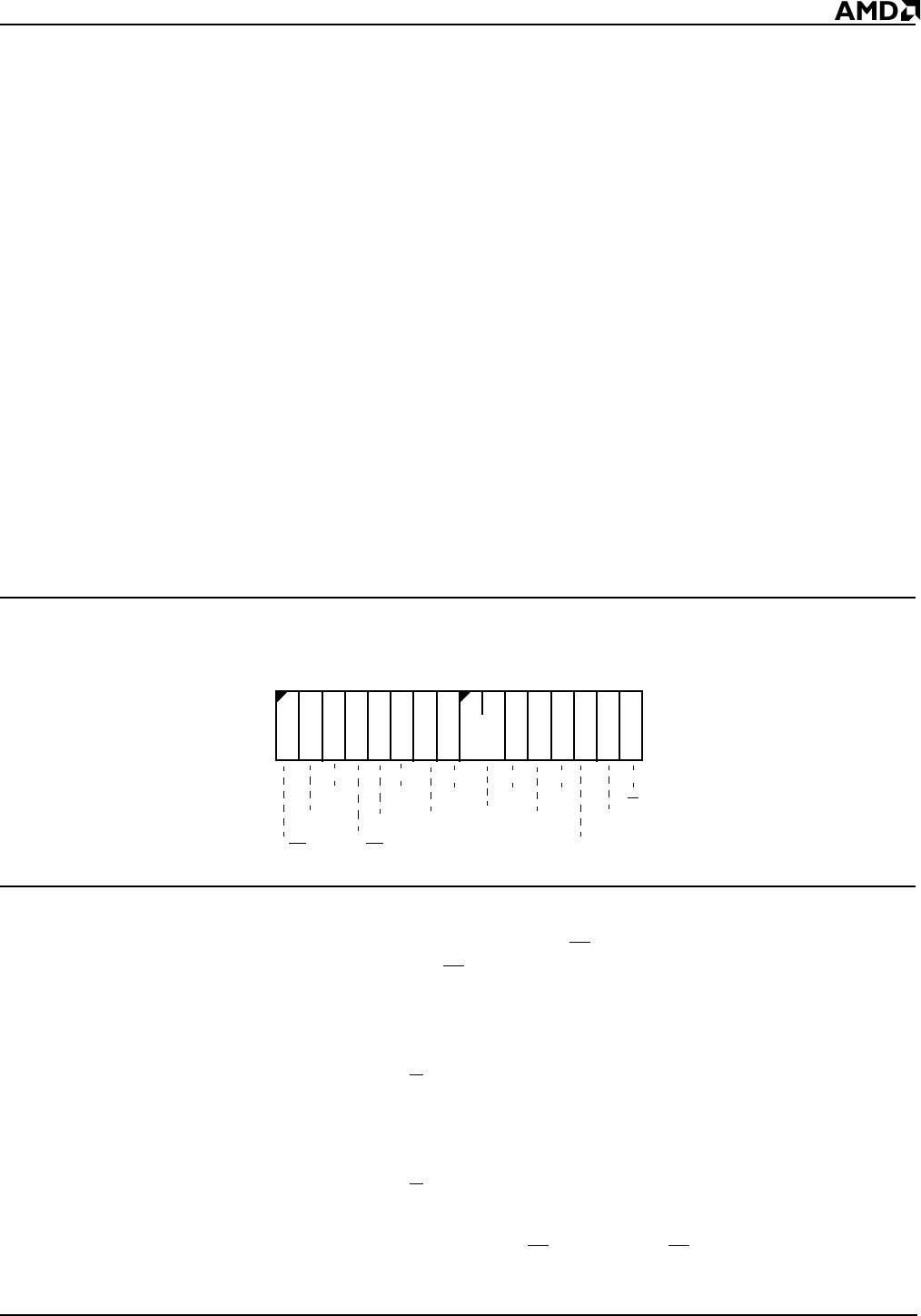

10.3.1 DMA Control Registers (D0CON, Offset CAh, D1CON, Offset DAh)

The DMA control registers (see Figure 10-2) determine the mode of operation for the DMA

channels. These registers specify the following options:

n Whether the destination address is memory or I/O space

n Whether the destination address is incremented, decremented, or maintained constant

after each transfer

n Whether the source address is memory or I/O space

n Whether the source address is incremented, decremented, or maintained constant after

each transfer

n If DMA activity ceases after a programmed number of DMA cycles

n If an interrupt is generated after the last transfer

n The mode of synchronization

n The relative priority of one DMA channel with respect to the other DMA channel

n Whether timer 2 DMA requests are enabled or disabled

n Whether bytes or words are transferred

The DMA channel control registers can be changed while the channel is operating. Any

changes made during DMA operations affect the current DMA transfer.

Figure 10-2 DMA Control Registers (D0CON, D1CON, offsets CAh and DAh)

The value of D0CON and D1CON at reset is FFF9h.

Bit 15: Destination Address Space Select (DM/IO

)—Selects memory or I/O space for

the destination address. When DM/IO

is set to 1, the destination address is in memory

space. When set to 0, the destination address is in I/O space.

Bit 14: Destination Decrement (DDEC)—When DDEC is set to 1, the destination address

is automatically decremented after each transfer. The address decrements by 1 or 2,

depending on the byte/word bit (B

/W, bit 0). The address remains constant if the increment

and decrement bits are set to the same value (00b or 11b).

Bit 13: Destination Increment (DINC)—When DINC is set to 1, the destination address

is automatically incremented after each transfer. The address increments by 1 or 2,

depending on the byte/word bit (B

/W, bit 0). The address remains constant if the increment

and decrement bits are set to the same value (00b or 11b).

Bit 12: Source Address Space Select (SM/IO

)—When SM/IO is set to 1, the source

address is in memory space. When set to 0, the source address is in I/O space.

15

70

DM/IO

DINC

DDEC

SM/IO

SINC

SDEC

B/W

ST

CHG

Res

TC

INT

SYN

P

TDRQ