DMA Controller

10-1

CHAPTER

10

DMA CONTROLLER

10.1 OVERVIEW

Direct memory access (DMA) permits transfer of data between memory and peripherals

without CPU involvement. The DMA unit in the Am186ER and Am188ER microcontrollers

provides two high-speed DMA channels. Data transfers can occur between memory and I/O

spaces (e.g., memory to I/O) or within the same space (e.g., memory-to-memory or I/O-to-I/O).

Two bus cycles (a minimum of eight clocks) are necessary for each data transfer.

Either bytes or words can be transferred to or from even or odd addresses on the Am186ER.

The Am186ER does not support word DMA transfers to or from memory configured for 8-bit

accesses. The Am188ER microcontroller does not support word transfers.

Each channel accepts a DMA request from one of two sources: the channel request pin

(DRQ1–DRQ0) or Timer 2. The two DMA channels can be programmed with different

priorities to resolve simultaneous DMA requests, and transfers on one channel can interrupt

the other channel.

10.2 DMA OPERATION

The format of the DMA control block is shown in Table 10-1. Six registers in the peripheral

control block define the operation of each channel. The DMA registers consist of a 20-bit

source address (2 registers), a 20-bit destination address (2 registers), a 16-bit transfer

count register, and a 16-bit control register.

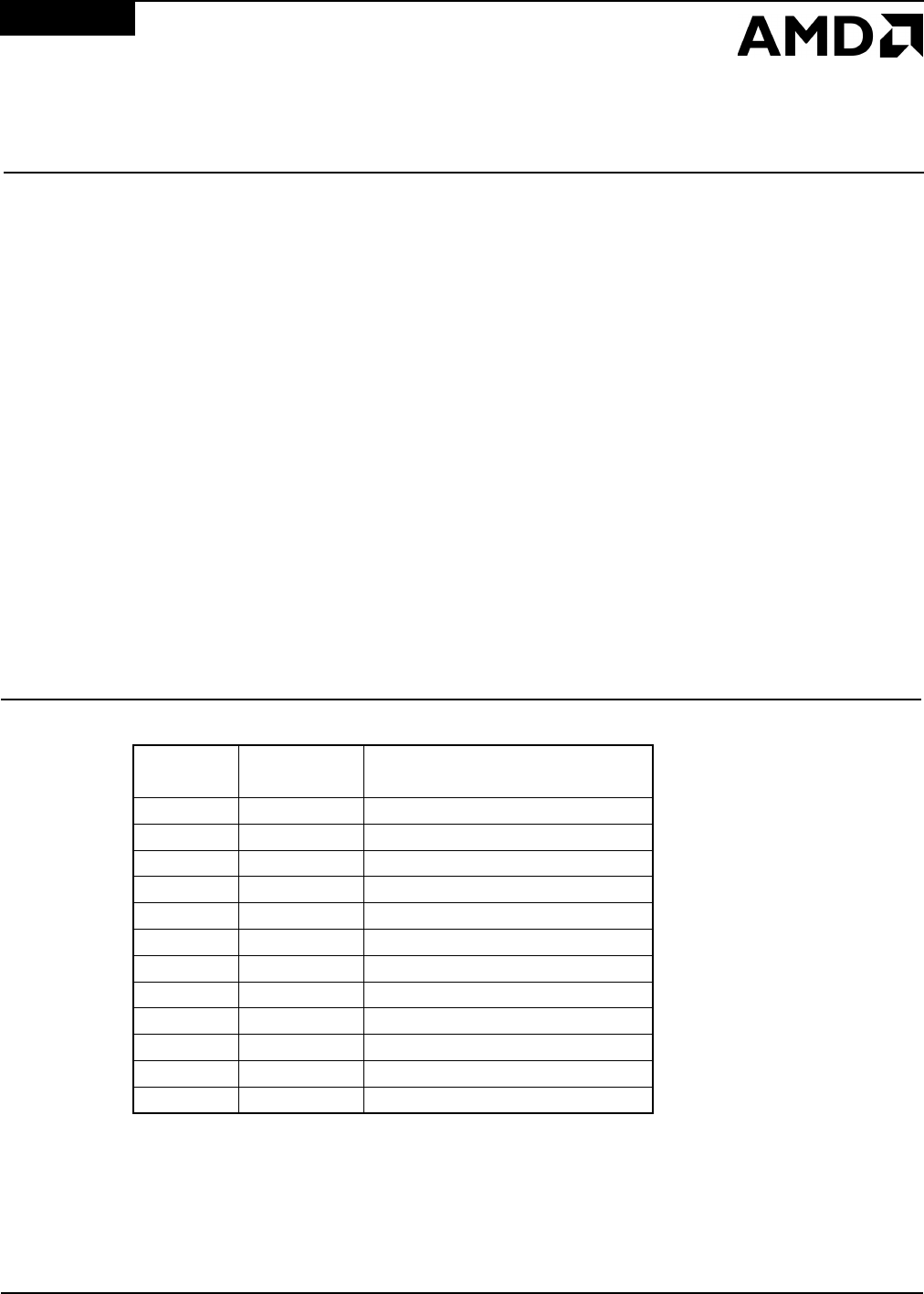

Table 10-1 DMA Controller Register Summary

The DMA transfer count register (DTC) specifies the number of DMA transfers to be

performed. Up to 64 Kbytes or 64 Kwords can be transferred with automatic termination.

The DMA control registers define the channel operations (see Figure 10-1). All registers

can be modified or altered during any DMA activity. Any changes made to these registers

are reflected immediately in DMA operation.

Offset from

PCB

Register

Mnemonic Register Name

CAh D0CON DMA 0 Control

DAh D1CON DMA 1 Control

C8h D0TC DMA 0 Transfer Count

D8h D1TC DMA 1 Transfer Count

C6h D0DSTH DMA 0 Destination Address High

D6h D1DSTH DMA 1 Destination Address High

C4h D0DSTL DMA 0 Destination Address Low

D4h D1DSTL DMA 1 Destination Address Low

C2h D0SRCH DMA 0 Source Address High

D2h D1SRCH DMA 1 Source Address High

C0h D0SRCL DMA 0 Source Address Low

D0h D1SRCL DMA 1 Source Address Low