Peripheral Control Block

4-5

4.1.2 Reset Configuration Register (RESCON, Offset F6h)

The Reset Configuration (RESCON) Register (see Figure 4-3) in the peripheral control

block latches system-configuration information that is presented to the processor on the

address/data bus (AD15–AD0 for the Am186ER or AO15–AO8 and AD7–AD1 for the

Am188ER) during the rising edge of reset. The interpretation of this information is system

specific. The processor does not impose any predetermined interpretation, but simply

provides a means for communicating this information to software.

When the RES

input is asserted Low, the contents of the address/data bus are written into

the RESCON Register. The system can place configuration information on the address/

data bus using weak external pullup or pulldown resistors, or using an external driver that

is enabled during reset. The processor does not drive the address/data bus during reset.

For example, the RESCON Register could be used to provide the software with the position

of a configuration switch in the system. Using weak external pullup and pulldown resistors

on the address and data bus, the system could provide the microcontroller with a value

corresponding to the position of a jumper during a reset.

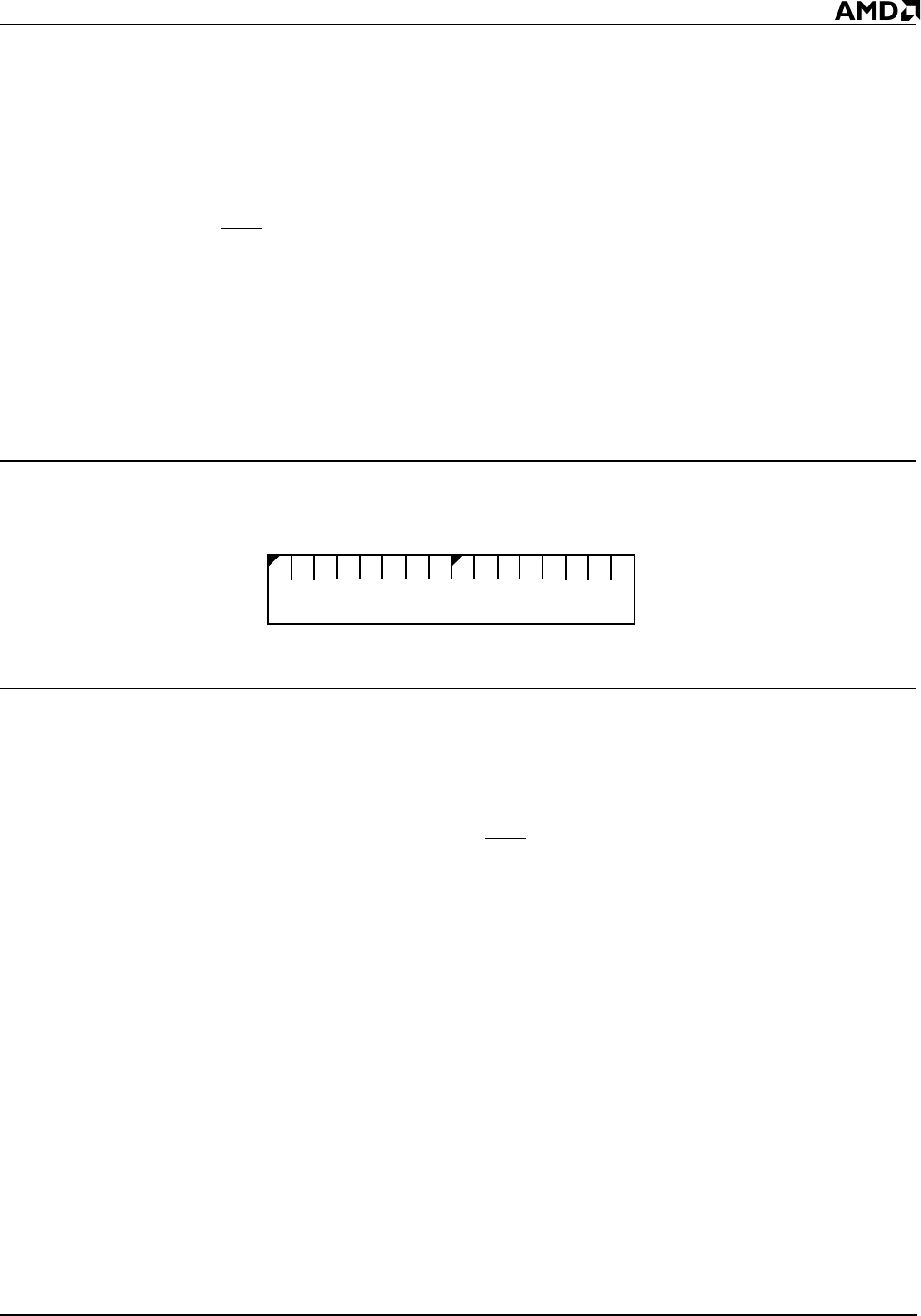

Figure 4-3 Reset Configuration Register (RESCON, offset F6h)

On reset, the RESCON Register is set to the value found on AD15–AD0.

Bits 15–0: Reset Configuration (RC)—There is a one-to-one correspondence between

address/data bus signals during the reset and the Reset Configuration Register’s bits. On

the Am186ER microcontroller, AD15 corresponds to bit 15 of the Reset Configuration

Register, and so on. On the Am188ER microcontroller, AO15 corresponds to register bit

15, and AD7 corresponds to bit 7. Once RES

is deasserted, the RESCON Register holds

its value. This value can be read by software to determine the configuration information.

The contents of the RESCON Register are read-only and remain valid until the next

processor reset.

15

70

RC