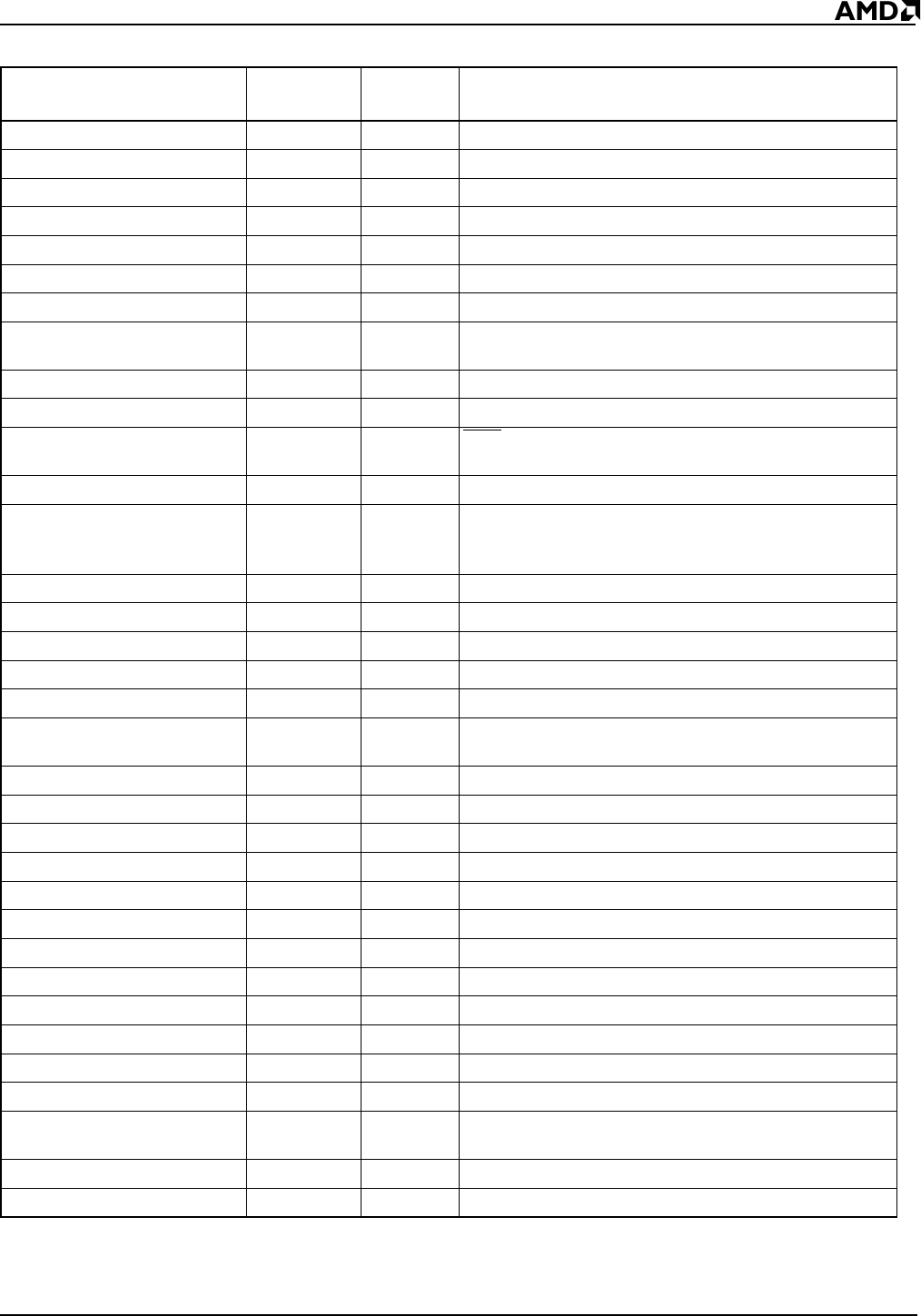

Peripheral Control Block

4-9

Table 4-2 Initial Register State After Reset

Note:

Registers not listed in this table are undefined at reset.

Register Name Mnemonic

Value at

Reset Comments

Processor Status Flags F F002h Interrupts disabled

Instruction Pointer IP 0000h

Code Segment CS FFFFh Boot address is FFFF0h

Data Segment DS 0000h DS = ES = SS = 0000h

Extra Segment ES 0000h

Stack Segment SS 0000h

Processor Release Level PRL XXxxh PRL XX = Revision (lower half-word is undefined)

Peripheral Control Block

Relocation

RELREG 20FFh Peripheral control block located at FF00h in I/O space

and interrupt controller in Master mode

Memory Partition MDRAM 0000h Refresh base address is 00000h

Enable RCU EDRAM 0000h Refresh disabled, counter = 0

Upper Memory Chip Select UMCS F03Bh UCS

active for 64K from F0000h to FFFFFh, 3 wait

states, external Ready signal required

Low Memory Chip Select LMCS Undefined

Serial Port Control SPCT 0000h Serial port interrupts disabled, no loopback, no break,

BRKVAL low, no parity, word length = 7, 1 stop bit,

transmitter and receiver disabled

PIO Direction 1 PIODIR1 FFFFh

PIO Mode 1 PIOMODE1 0000h

PIO Direction 0 PIODIR0 FC0Fh

PIO Mode 0 PIOMODE0 0000h

Serial Port Interrupt Control SPICON 001Fh Serial port interrupt masked, priority 7

Watchdog Timer Interrupt

Control

WDCON 000Fh Watchdog timer interrupt masked, priority 7

INT4 Control I4CON 000Fh Int4 interrupt masked, edge-triggered, priority 7

INT3 Control I3CON 000Fh Int3 interrupt masked, edge-triggered, priority 7

INT2 Control I2CON 000Fh Int2 interrupt masked, edge-triggered, priority 7

INT1 Control I1CON 000Fh Int1 interrupt masked, edge-triggered, priority 7

INT0 Control I0CON 000Fh Int0 interrupt masked, edge-triggered, priority 7

DMA1 Interrupt Control DMA1CON 000Fh DMA1 interrupts masked, edge-triggered, priority 7

DMA0 Interrupt Control DMA0CON 000Fh DMA0 interrupts masked, edge-triggered, priority 7

Timer Interrupt Control TCUCON 000Fh Timer interrupts masked, edge-triggered, priority 7

In-Service INSERV 0000h No interrupts are in-service

Priority Mask PRIMSK 0007h Allow all interrupts based on priority

Interrupt Mask IMASK 07FDh All interrupts masked (off)

Synchronous Serial Control SSC 0000h SCLK = 1/2 CLKOUTA, no data enabled

Synchronous Serial Status SSS 0000h Synchronous serial port not busy, no errors, no transmit

or receive completed.

DMA 1 Control D1CON FFF9h

DMA 0 Control D0CON FFF9h