Asynchronous Serial Port

11-4

11.2.2 Serial Port Status Register (SPSTS, Offset 82h)

The Serial Port Status register indicates the status of the transmit and receive sections of

the serial port. The format of the Serial Port Status register is shown in Figure 11-2.

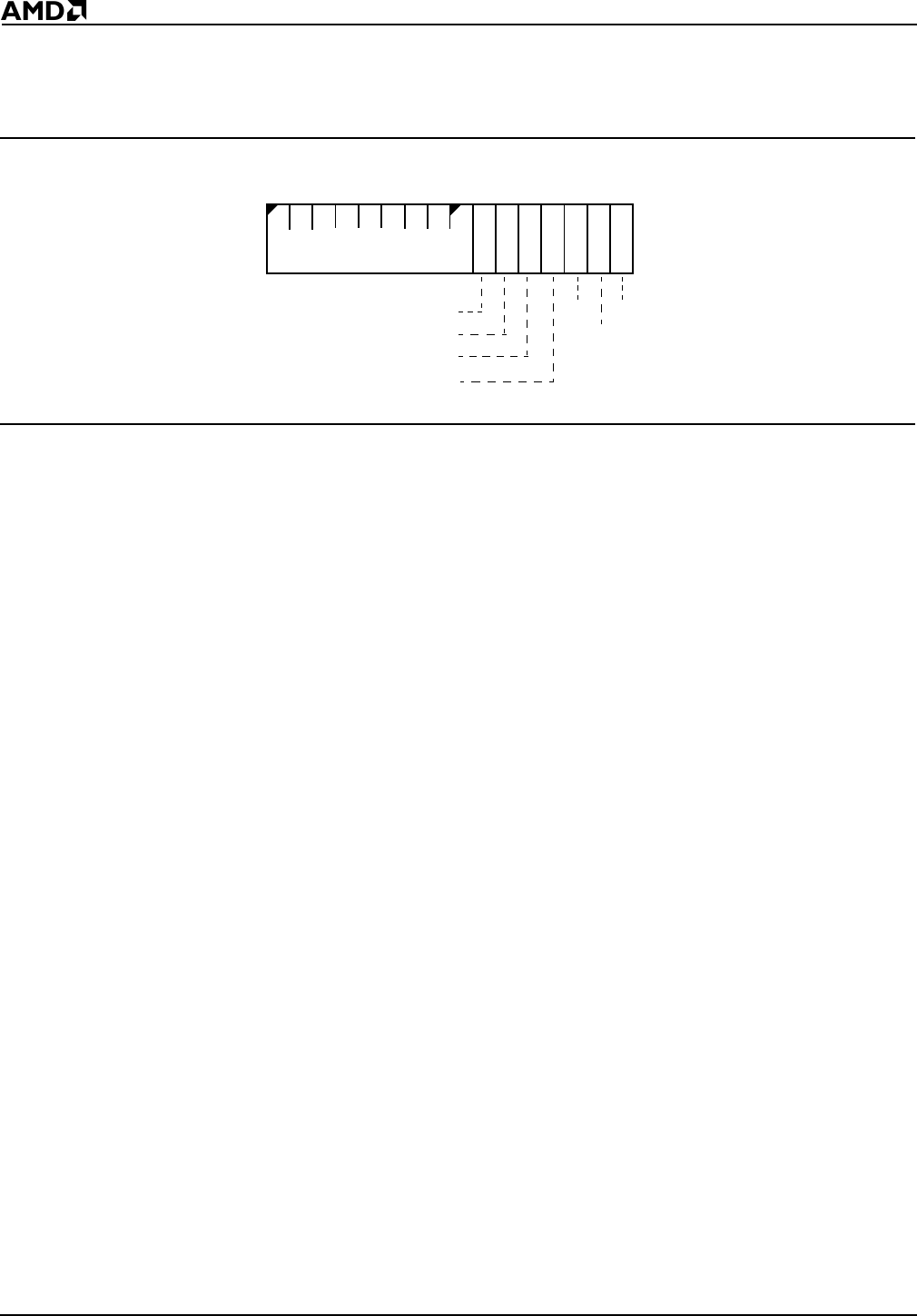

Figure 11-2 Serial Port Status Register (SPSTS, offset 82h)

Bits 15–7: Reserved—Set to 0.

Bit 6: Transmitter Empty (TEMT)—The TEMT bit is 1 when the transmitter has no data

to transmit and the transmit shift register is empty. This indicates to software that it is safe

to disable the transmit section. This bit is read-only.

Bit 5: Transmit Holding Register Empty (THRE)—When the THRE bit is 1, the transmit

holding register contains invalid data and can be written with data to be transmitted. When

the THRE bit is 0, the transmit holding register should not be written because it contains

valid data that has not yet been copied to the transmit shift register for transmission.

If transmit interrupts are enabled by the TMODE and TXIE fields, a serial port interrupt

request is generated when the THRE bit is 1. The THRE bit is reset automatically by writing

the transmit holding register. This bit is read-only, allowing other bits of the Serial Port

Status register to be written (i.e., resetting the BRKI bit) without interfering with the current

data request.

Bit 4: Receive Data Ready (RDR)—When the RDR bit is 1, the receive buffer register

contains data that can be read. When the RDR bit is 0, the receive buffer register does not

contain valid data. This bit is read-only.

If receive interrupts are enabled by the RMODE and RXIE fields, a serial port interrupt

request is generated when the THRE bit is 1. Reading the receive buffer register resets

the RDR bit.

Bit 3: Break Interrupt (BRKI)—The BRKI bit is set to indicate that a break has been

received. If the RSIE bit is 1, the BRKI bit being set causes a serial port interrupt request.

The BRKI bit should be reset by software.

Bit 2: Framing Error (FER)—The FER bit is set to indicate that a framing error occurred

during reception of data. If the RSIE bit is 1, the FER bit being set causes a serial port

interrupt request. The FER bit should be reset by software.

Bit 1: Parity Error (PER)—The PER bit is set to indicate that a parity error occurred during

reception of data. If the RSIE bit is 1, the PER bit being set causes a serial port interrupt

request. The PER bit should be reset by software.

Bit 0: Overrun Error (OER)—The OER bit is set when an overrun error occurs during

reception of data. If the RSIE bit is 1, the OER bit being set causes a serial port interrupt

request. The OER bit should be reset by software.

15

70

Reserved

TEMT

THRE

RDR

BRKI

OER

PER

FER