Timer Control Unit

9-5

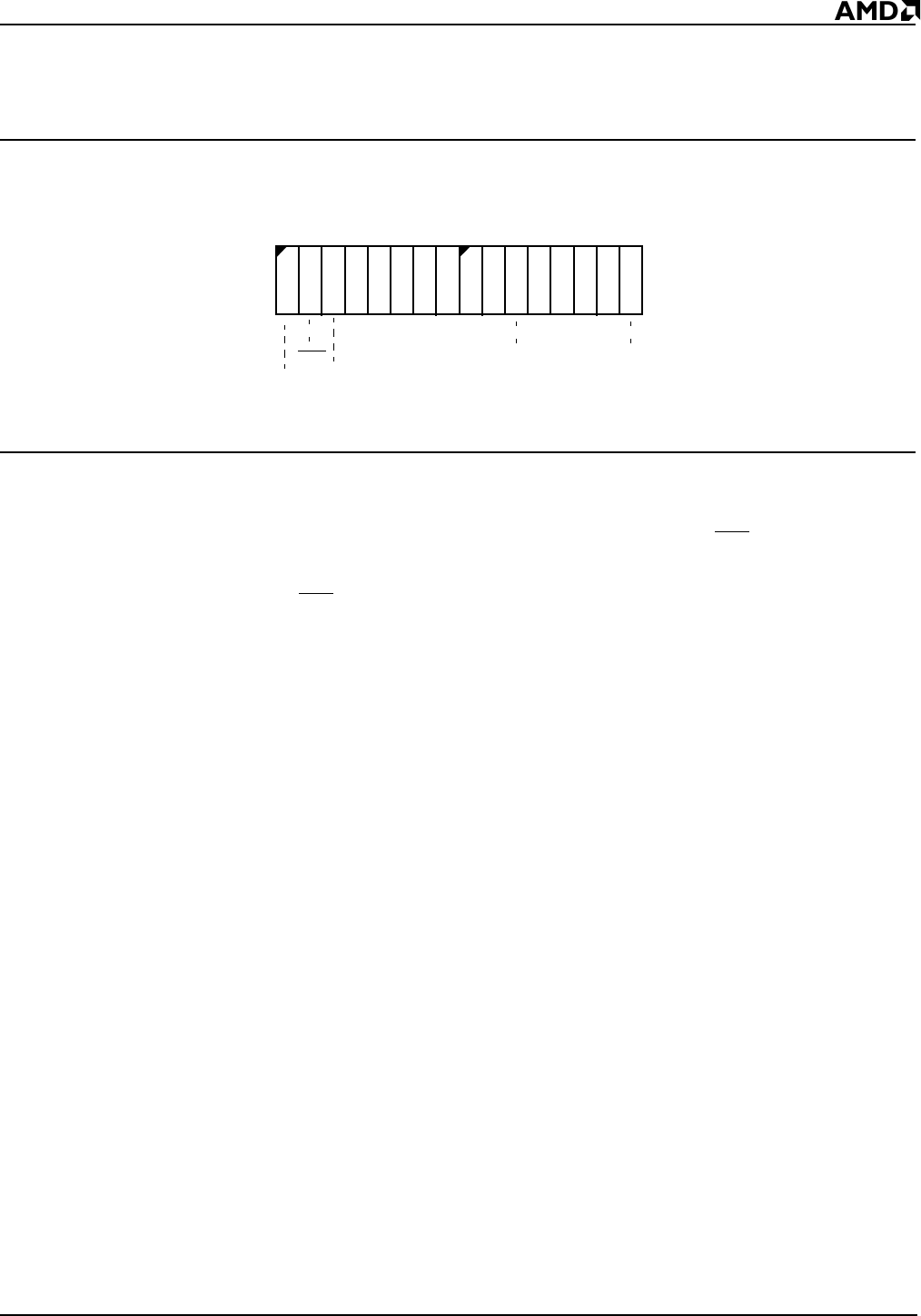

9.2.3 Timer 2 Mode and Control Register

(T2CON, Offset 66h)

This register controls the functionality of timer 2. See Figure 9-2.

Figure 9-2 Timer 2 Mode and Control Register (T2CON, offset 66h)

The value of T2CON at reset is 0000h.

Bit 15: Enable Bit (EN)—When EN is set to 1, the timer is enabled. When set to 0, the

timer is inhibited from counting. This bit can only be written with the INH

bit set at the same

time.

Bit 14: Inhibit Bit (INH

)—Allows selective updating of enable (EN) bit. When INH is set to

1 during a write, EN can be modified on the same write. When INH is set to 0 during a write,

writes to EN are ignored. This bit is not stored and is always read as 0.

Bit 13: Interrupt Bit (INT)—When INT is set to 1, an interrupt request is generated when

the count register equals a maximum count. When INT is set to 0, the timer will not issue

interrupt requests. If the EN enable bit is cleared after an interrupt request has been

generated, but before the pending interrupt is serviced, the interrupt request remains active.

Bits 12–6: Reserved—Set to 0.

Bit 5: Maximum Count Bit (MC)—The MC bit is set to 1 when the timer reaches its

maximum count. This bit is set regardless of the timer interrupt-enable bit. The MC bit can

be used to monitor timer status through software polling instead of through interrupts.

Bits 4–1: Reserved—Set to 0.

Bit 0: Continuous Mode Bit (CONT)—When CONT is set to 1, it causes the associated

timer to run continuously. When set to 0, EN is cleared after each timer count sequence

and the timer halts on reaching the maximum count.

15

70

EN

INT

INH

0

MC

CONT

0000000000