5-3

STANDARD AND PTS INTERRUPTS

Figure 5-1 illustrates the interrupt processing flow. In this flow diagram, “INT_MASK” repre-

sents both the INT_MASK and INT_MASK1 registers, and “INT_PEND” represents both the

INT_PEND and INT_PEND1 registers.

5.2 INTERRUPT SIGNALS AND REGISTERS

Table 5-1 describes the external interrupt signals and Table 5-2 describes the control and status

registers for both the interrupt controller and PTS.

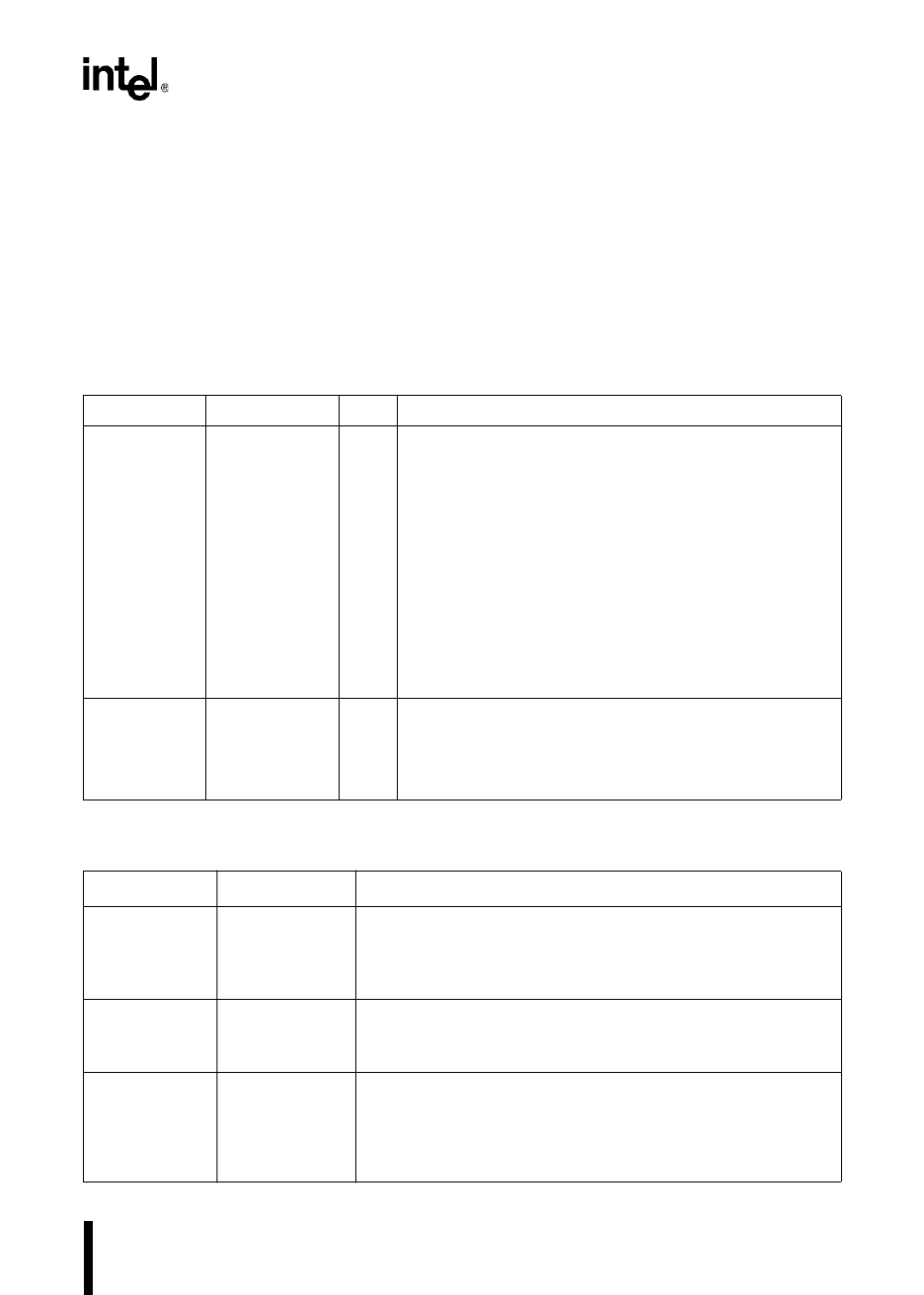

Table 5-1. Interrupt Signals

Port Pin Interrupt Signal Type Description

— EXTINT I External Interrupt

This programmable interrupt is controlled by the

WG_PROTECT register. This register controls whether the

interrupt is edge triggered or sampled and whether a rising

edge/high level or falling edge/low level activates the

interrupt.

In powerdown mode, asserting the EXTINT signal for at least

50 ns causes the device to resume normal operation. The

interrupt need not be enabled. If the EXTINT interrupt is

enabled, the CPU executes the interrupt service routine.

Otherwise, the CPU executes the instruction that immediately

follows the command that invoked the power-saving mode.

In idle mode, asserting any enabled interrupt causes the

device to resume normal operation.

— NMI I Nonmaskable Interrupt

In normal operating mode, a rising edge on NMI generates a

nonmaskable interrupt. NMI has the highest priority of all

prioritized interrupts. Assert NMI for greater than one state

time to guarantee that it is recognized.

Table 5-2. Interrupt and PTS Control and Status Registers

Mnemonic Address Description

INT_MASK

INT_MASK1

0008H

0013H

Interrupt Mask Registers

These registers enable/disable each maskable interrupt (that is,

each interrupt except unimplemented opcode, software trap, and

NMI).

INT_PEND

INT_PEND1

0009H

0012H

Interrupt Pending Registers

The bits in this register are set by hardware to indicate that an

interrupt is pending.

PI_MASK 1FBCH Peripheral Interrupt Mask

The bits in this register enable and disable (mask) the timer 1 and 2

overflow/underflow interrupt requests, the waveform generator

interrupt request (MC, MD), the EPA compare-only channel 5

interrupt request (MD), and the serial port error interrupts (MH).