8XC196MC, MD, MH USER’S MANUAL

7-6

During a reception, the RI flag in SPx_STATUS is set after the stop bit is sampled. The RIx pend-

ing bit in the interrupt pending register is set immediately before the RI flag is set. During a trans-

mission, the TI flag is set immediately after the end of the last (eighth) data bit is transmitted. The

TIx pending bit in the interrupt pending register is generated when the TI flag in SPx_STATUS is

set.

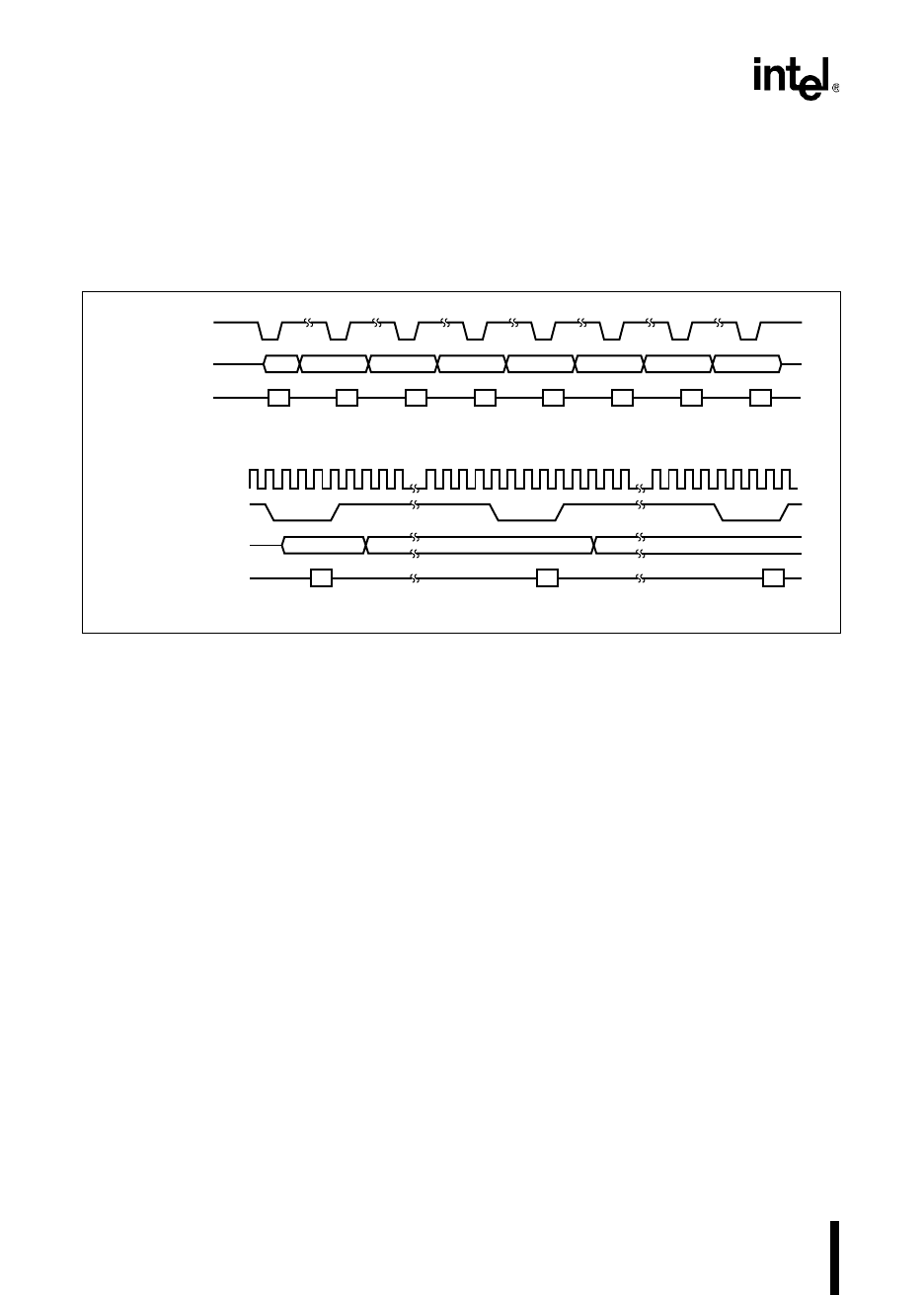

Figure 7-3. Mode 0 Timing

7.3.1.2 Mode 4

Mode 4 is an enhanced synchronous mode that is similar to mode 0 in many ways, but there are

three main differences:

• In mode 0, TXDx inputs or outputs the clock signal and RXDx transmits or receives data. In

mode 4, TXDx transmits data, RXDx receives data, and the SCLKx# pin inputs or outputs

the clock signal.

• For mode 4, a direction bit (DIR) was added to the SPx_CON register. This bit controls

whether SCLKx# outputs the internal shift clock or inputs an external shift clock.

• In mode 0, RXDx must be enabled to start a transmission (because it must transmit the

data). In mode 4, TXDx transmits the data, so the RXDx status is unrelated to transmissions.

Writing to SBUFx_TX starts a transmission regardless of whether RXDx is enabled.

In mode 4, SCLKx# outputs a set of eight clock pulses while TXDx transmits data, or SCLKx#

accepts a set of eight clock pulses while RXDx receives data. Data is transferred eight bits at a

time with the least-significant bit first. When SCLKx# is in output mode, its timing is identical to

that of TXDx shown in Figure 7-3. When SCLKx# is in input mode, the input shift clock signal

is internally synchronized with the internal clock.

TXD

RXD (out)

RXD (in)

D0

D0

D1 D2 D3 D4 D5 D6 D7

D1 D2 D3 D4 D5 D6 D7

D0

D0

D1 D2

D1

XTAL1

TXD

RXD (out)

RXD (in)

Expanded:

A0109-02