C-37

REGISTERS

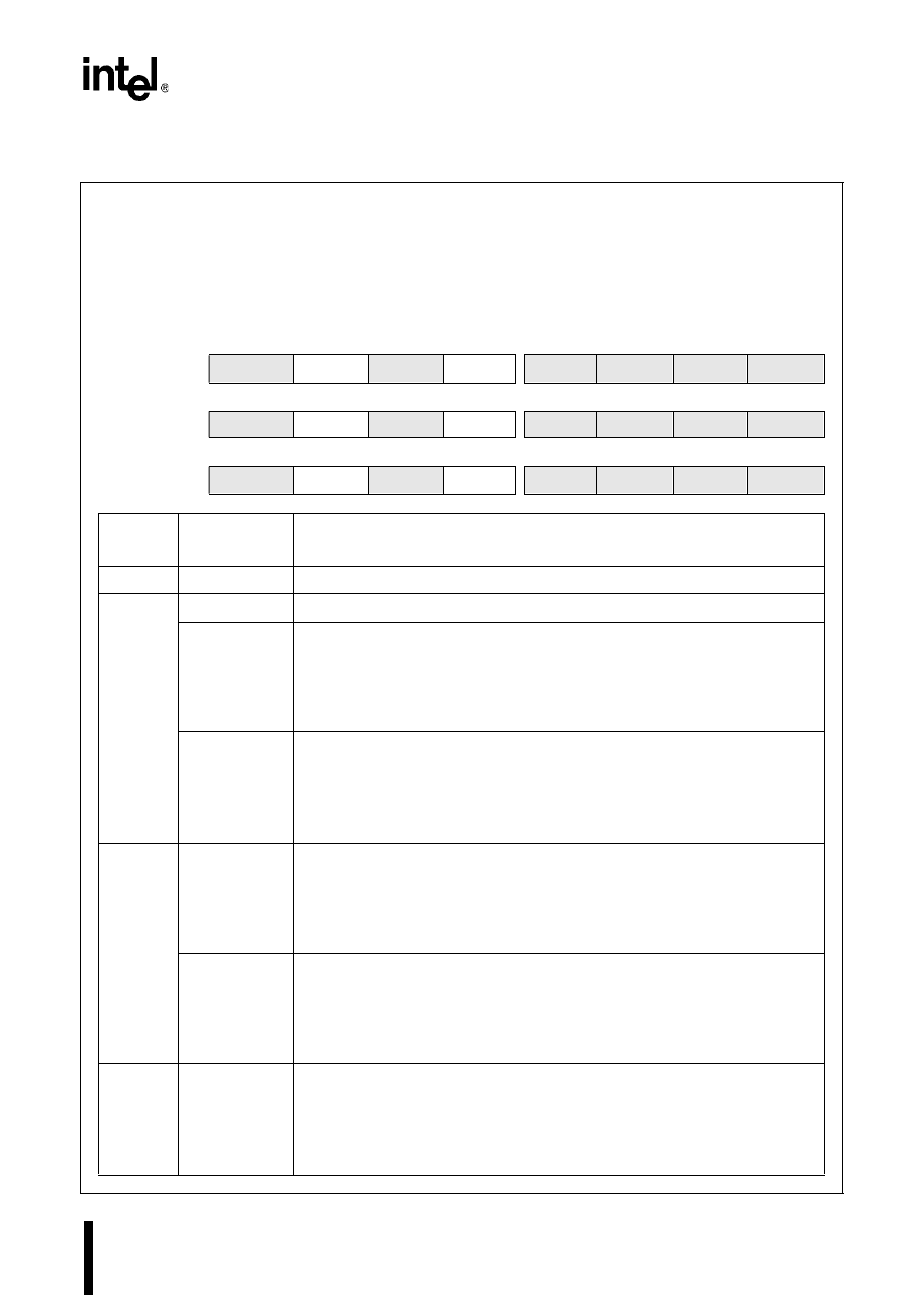

PI_PEND

PI_PEND

Address:

Reset State:

1FBEH

AAH

When hardware detects a pending peripheral or timer interrupt, it sets the corresponding bit in the

interrupt pending (INT_PEND or INT_PEND1) registers and the peripheral interrupt pending

(PI_PEND) register. When the vector is taken, the hardware clears the INT_PEND/INT_PEND1

pending bit. Reading this register clears all the PI_PEND bits. Software can generate an interrupt by

setting a PI_PEND bit.

7 0

8XC196MC

———WG —OVRTM2 — OVRTM1

7 0

8XC196MD

— COMP5 —WG —OVRTM2 — OVRTM1

7 0

8XC196MH

—SP1—SP0 —OVRTM2 — OVRTM1

Bit

Number

Bit

Mnemonic

Function

7, 5, 3, 1 — Reserved. These bits are undefined.

6 — (MC) Reserved. This bit is undefined.

COMP5 (MD) EPA Compare Channel 5

When set, this bit indicates a pending EPA compare channel 5 interrupt.

The EPA compare channel 5 and the waveform generator interrupts are

associated with the peripheral interrupt (PI). Setting INT_MASK1.5

enables PI. Setting PI_MASK.6 enables COMP5.

SP1 (MH) Serial Port 1 Error

When set, this bit indicates a pending serial port 1 error interrupt.

The serial port 1 and 0 error interrupts are associated with the serial port

interrupt (SPI). Setting INT_MASK1.4 enables SPI. Setting PI_MASK.6

enables SP1.

4 WG (MC, MD) Waveform Generator

When set, this bit indicates a pending waveform generator interrupt.

The waveform generator and the EPA compare channel 5 interrupts are

associated with the peripheral interrupt (PI). Setting INT_MASK1.5

enables PI. Setting PI_MASK.5 enables WG.

SP0 (MH) Serial Port 0 Error

When set, this bit indicates a pending serial port 0 error interrupt.

The serial port 0 and 1 error interrupts are associated with the serial port

interrupt (SPI). Setting INT_MASK1.4 enables SPI. Setting PI_MASK.4

enables SP0.

2 OVRTM2 Timer 2 Overflow/Underflow

When set, this bit indicates a pending timer 2 overflow/underflow interrupt.

The timer 2 and timer 1 overflow/underflow interrupts are associated with

the overflow/underflow timer interrupt (OVRTM). Setting INT_MASK.0

enables OVRTM. Setting PI_MASK.2 enables OVRTM2.