13-11

MINIMUM HARDWARE CONSIDERATIONS

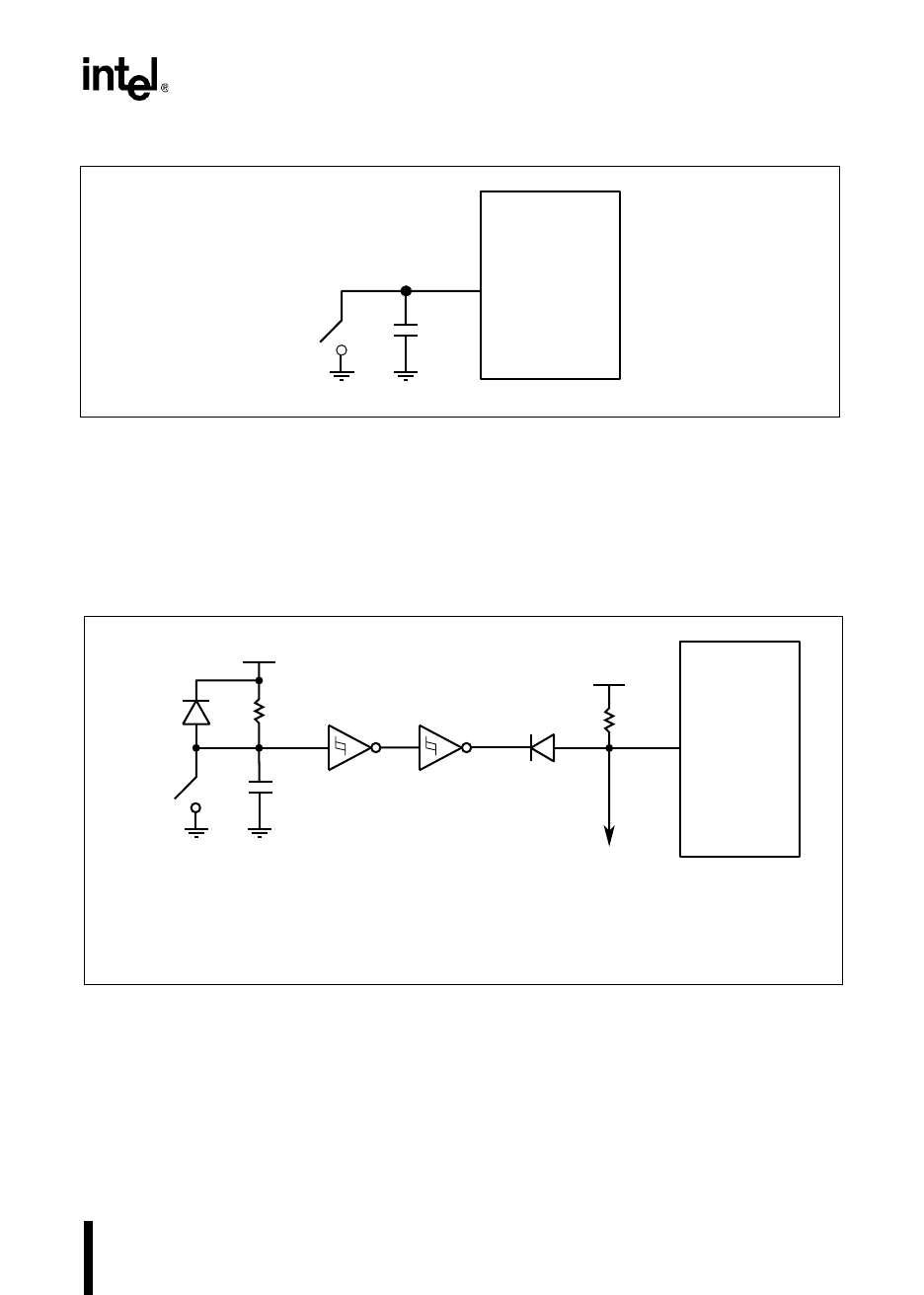

Figure 13-10. Minimum Reset Circuit

Other devices in the system may not be reset because the capacitor will keep the voltage above

V

IL

. Since RESET# is asserted for only 16 state times, it may be necessary to lengthen and buffer

the system-reset pulse. Figure 13-11 shows an example of a system-reset circuit. In this example,

D2 creates a wired-OR gate connection to the reset pin. An internal reset, system power-up, or

SW1 closing will generate the system-reset signal.

Figure 13-11. Example of a System Reset Circuit

RESET#

+

4.7 µF

A0276-02

MCS

®

96

Microcontroller

RESET#

System reset signal

to external circuitry

(1)

Schmitt Triggers

Notes:

1. D1 provides a faster cycle time for repetitive power-on resets.

2. Optional pull-up for faster recovery.

R

C

4.7 kΩ

(2)

D2

SW1

D1

A0277-03

V

CC

V

CC

MCS

®

96

Microcontroller