8XC196MC, MD, MH USER’S MANUAL

14-4

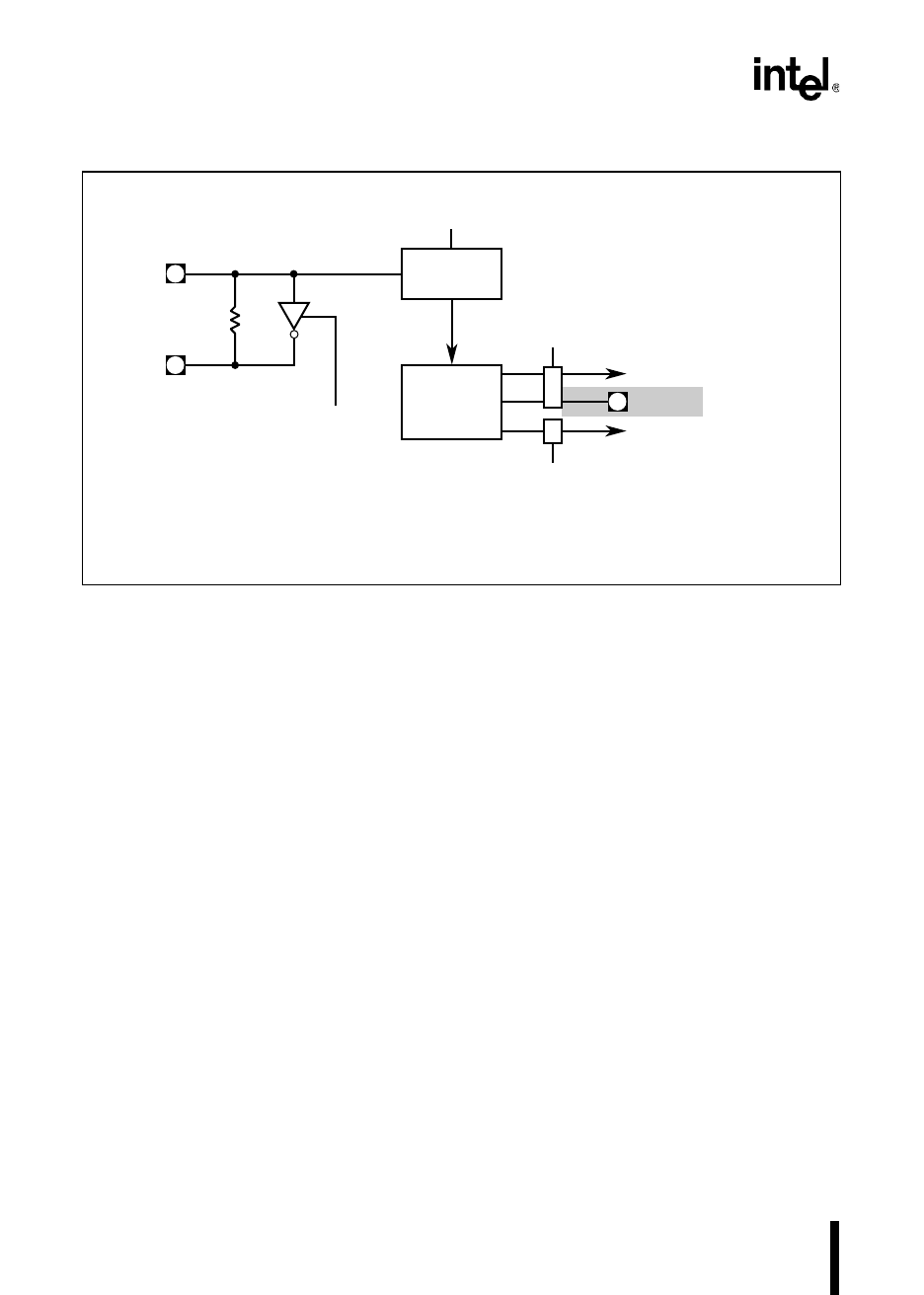

Figure 14-1. Clock Control During Power-saving Modes

14.3 IDLE MODE

In idle mode, the device’s power consumption decreases to approximately 40% of normal con-

sumption. Internal logic holds the CPU clocks at logic zero, causing the CPU to stop executing

instructions. Neither the peripheral clocks nor CLKOUT are affected, so the special-function reg-

isters (SFRs) and register RAM retain their data and the peripherals and interrupt system remain

active. Tables in Appendix B list the values of the pins during idle mode (see Table B-8 on page

B-23 for the 8XC196MC and 8XC196MD or Table B-9 on page B-25 for the 8XC196MH).

A3115-02

Clock

Generators

CPU Clocks (PH1, PH2)

Divide-by-two

Circuit

XTAL1

XTAL2

F

XTAL1

Disable

Oscillator

(Powerdown)

Peripheral Clocks (PH1, PH2)

CLKOUT

Disable Clocks

(Powerdown)

Disable Clocks

(Idle, Powerdown)

NOTE: The CLKOUT pin is unique to the 8XC196MC and MD.

Disable Clock Input

(Powerdown)