8XC196MC, MD, MH USER’S MANUAL

A-4

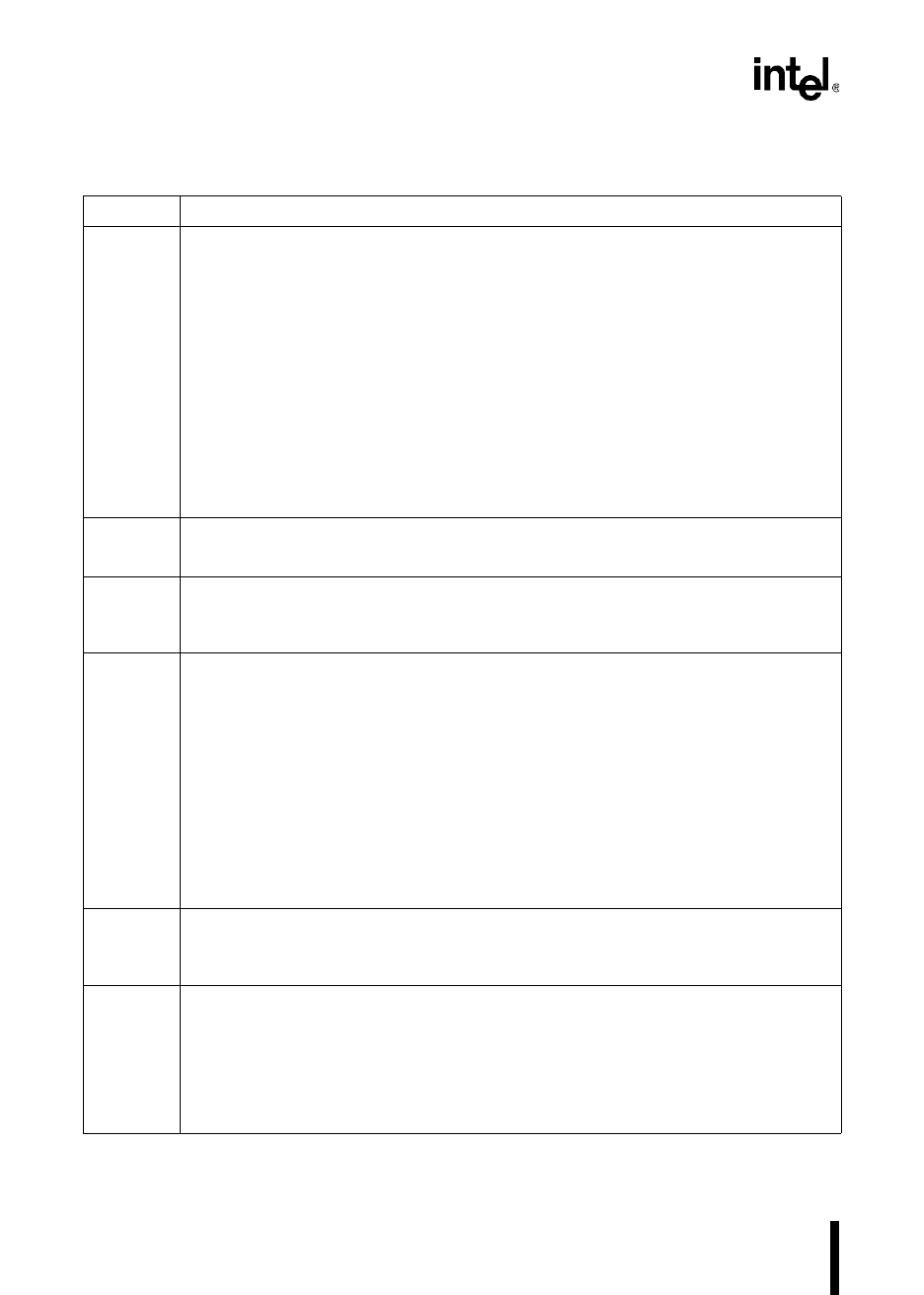

Table A-2. Processor Status Word (PSW) Flags

Mnemonic Description

C The carry flag is set to indicate an arithmetic carry from the MSB of the ALU or the state of

the last bit shifted out of an operand. If a subtraction operation generates a borrow, the carry

flag is cleared.

C Value of Bits Shifted Off

0 < ½ LSB

1 ≥ ½ LSB

Normally, the result is rounded up if the carry flag is set. The sticky bit flag allows a finer

resolution in the rounding decision.

C ST Value of Bits Shifted Off

00 = 0

0 1 > 0 and < ½ LSB

10 = ½ LSB

1 1 > ½ LSB and < 1 LSB

N The negative flag is set to indicate that the result of an operation is negative. The flag is

correct even if an overflow occurs. For all shift operations and the NORML instruction, the

flag is set to equal the most-significant bit of the result, even if the shift count is zero.

ST The sticky bit flag is set to indicate that, during a right shift, a “1” has been shifted into the

carry flag and then shifted out. This bit is undefined after a multiply operation. The sticky bit

flag can be used with the carry flag to allow finer resolution in rounding decisions. See the

description of the carry (C) flag for details.

V The overflow flag is set to indicate that the result of an operation is too large to be

represented correctly in the available space.

For shift operations, the flag is set if the most-significant bit of the operand changes during

the shift. For divide operations, the quotient is stored in the low-order half of the destination

operand and the remainder is stored in the high-order half. The overflow flag is set if the

quotient is outside the range for the low-order half of the destination operand. (Chapter 3,

“Programming Considerations,” defines the operands and possible values for each.)

Instruction Quotient Stored in: V Flag Set if Quotient is:

DIVB Short-integer < –128 or > +127 (< 81H or > 7FH)

DIV Integer < –32768 or > +32767 (< 8001H or > 7FFFH)

DIVUB Byte > 255 (FFH)

DIVU Word > 65535 (FFFFH)

VT The overflow-trap flag is set when the overflow flag is set, but it is cleared only by the CLRVT,

JVT, and JNVT instructions. This allows testing for a possible overflow at the end of a

sequence of related arithmetic operations, which is generally more efficient than testing the

overflow flag after each operation.

Z The zero flag is set to indicate that the result of an operation was zero. For multiple-precision

calculations, the zero flag cannot be set by the instructions that use the carry bit from the

previous calculation (e.g., ADDC, SUBC). However, these instructions can clear the zero

flag. This ensures that the zero flag will reflect the result of the entire operation, not just the

last calculation. For example, if the result of adding together the lower words of two double

words is zero, the zero flag would be set. When the upper words are added together using

the ADDC instruction, the flag remains set if the result is zero and is cleared if the result is not

zero.