9-3

WAVEFORM GENERATOR

9.2 WAVEFORM GENERATOR SIGNALS AND REGISTERS

Table 9-1 describes the waveform generator’s signals, and Table 9-2 briefly describes the control

and status registers.

.

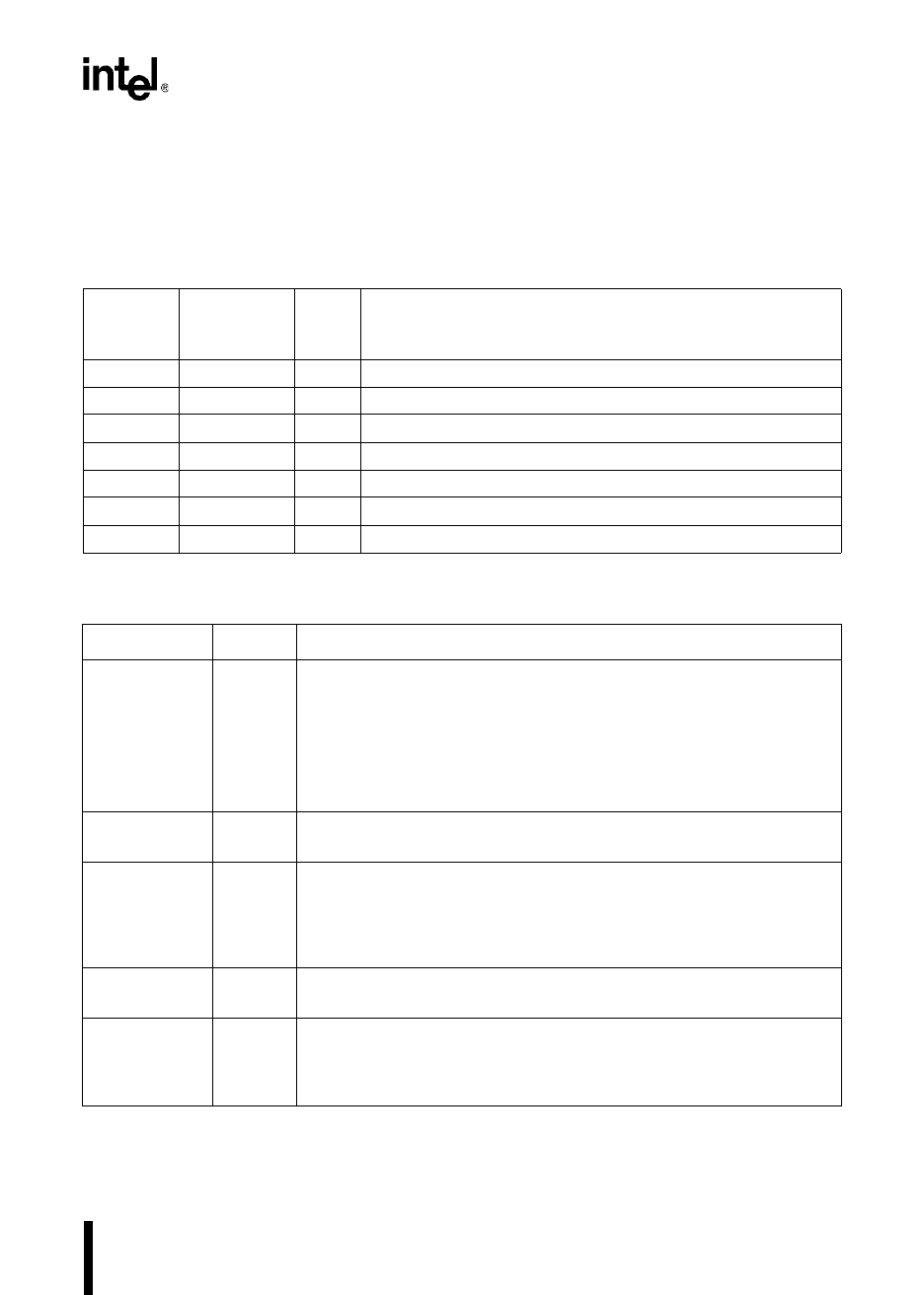

Table 9-1. Waveform Generator Signals

Port

Pin

Waveform

Generator

Signal

Type Description

P6.0 WG1# O Waveform generator phase 1 negative output.

P6.1 WG1 O Waveform generator phase 1 positive output.

P6.2 WG2# O Waveform generator phase 2 negative output.

P6.3 WG2 O Waveform generator phase 2 positive output.

P6.4 WG3# O Waveform generator phase 3 negative output.

P6.5 WG3 O Waveform generator phase 3 positive output.

— EXTINT I Input to the waveform generator’s protection circuitry.

Table 9-2. Waveform Generator Control and Status Registers

Mnemonic Address Description

INT_MASK1 0013H Interrupt Mask 1

The EXTINT bit enables or disables the EXTINT interrupt.

8XC196MH: The WG bit enables or disables the waveform generator

interrupt.

8XC196MC, MD: The PI bit enables or disables the multiplexed peripheral

interrupt. The corresponding bit in the PI_MASK register enables or disables

the individual sources of the peripheral interrupt.

INT_PEND1 0014H Interrupt Pending 1

Any set bit indicates a pending interrupt request.

PI_MASK

(MC, MD)

1FBCH Peripheral Interrupt Mask

8XC196MC, MD: The WG bit enables or disables the waveform generator

interrupt as one of the possible sources of the multiplexed peripheral

interrupt. The PI bit in INT_MASK1 must be set to enable the multiplexed

peripheral interrupt.

PI_PEND

(MC, MD)

1FBEH Peripheral Interrupt Pending

Any set bit indicates a pending interrupt request.

WG_COMP1

WG_COMP2

WG_COMP3

1FC2H

1FC4H

1FC6H

Waveform Generator Compare Buffers

Each phase compare buffer contains a value that is compared with the

counter value. The action that is performed when a match occurs depends

on the operating mode.