15-11

INTERFACING WITH EXTERNAL MEMORY

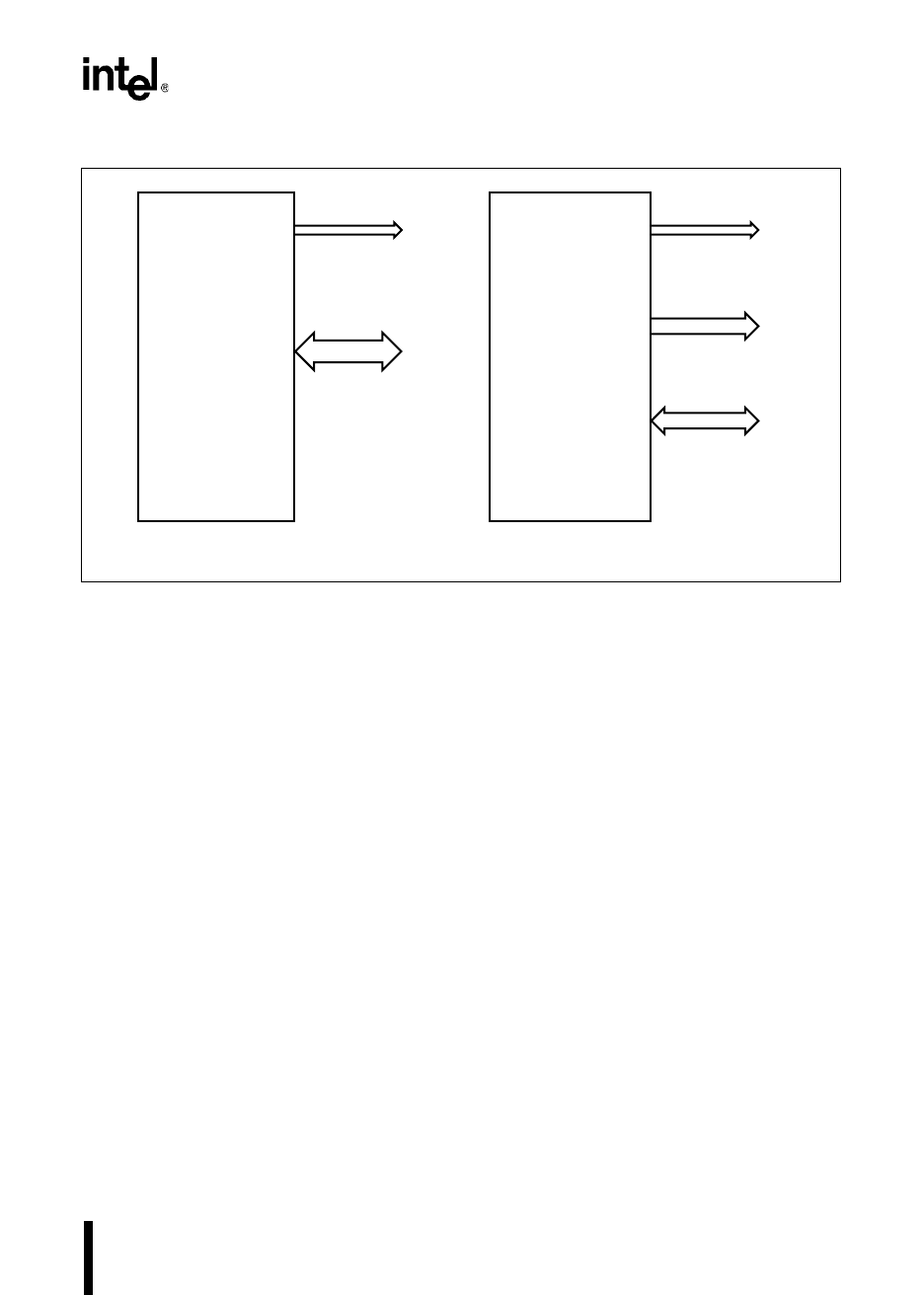

Figure 15-3. Multiplexing and Bus Width Options

After reset, but before the CCB fetch, the microcontroller is configured for 8-bit bus mode, re-

gardless of the BUSWIDTH input. The upper address lines (AD15:8) are weakly driven through-

out the CCB0 and CCB1 bus cycles. To prevent bus contention, neither pull-ups nor pull-downs

should be used on AD15:8. Also, the upper bytes of the CCB words (locations 2019H and

201BH) should be loaded with 20H. If the external memory outputs 20H on its high byte, there

will be no bus contention.

After the CCBs are loaded into the CCRs, the values of BW0 and BW1 define the data bus width

as either a fixed 8-bit, a fixed 16-bit, or a dynamic 16-bit/8-bit bus width controlled by the

BUSWIDTH signal. (The BW0 and BW1 bits are defined in Figures 15-1 and 15-2.)

If BW0 is clear and BW1 is set, the bus controller is locked into an 8-bit bus mode. In comparing

an 8-bit bus system to a 16-bit bus system, expect some performance degradation. In a 16-bit bus

system, a word fetch is done with a single word fetch. However, in an 8-bit bus system, a word

fetch takes an additional bus cycle because it must be done with two byte fetches.

If BW0 is set and BW1 is clear, the bus controller is locked into a 16-bit bus mode. If both BW0

and BW1 are set, the BUSWIDTH signal controls the bus width. The bus is 16 bits wide when

BUSWIDTH is high, and 8 bits wide when BUSWIDTH is low. The BUSWIDTH signal is sam-

pled after the address is on the bus, as shown in Figures 15-4 and 15-5.

Bus Control

16-bit Multiplexed

Address/Data

AD15:0

(Ports 4 and 3)

8XC196

Bus Control

AD15:8

(Port 4)

8XC196

8-bit Multiplexed

Address/Data

8-bit Address

High

AD7:0

(Port 3)

8-bit Bus16-bit Bus

A3068-01