5-17

PROGRAMMING

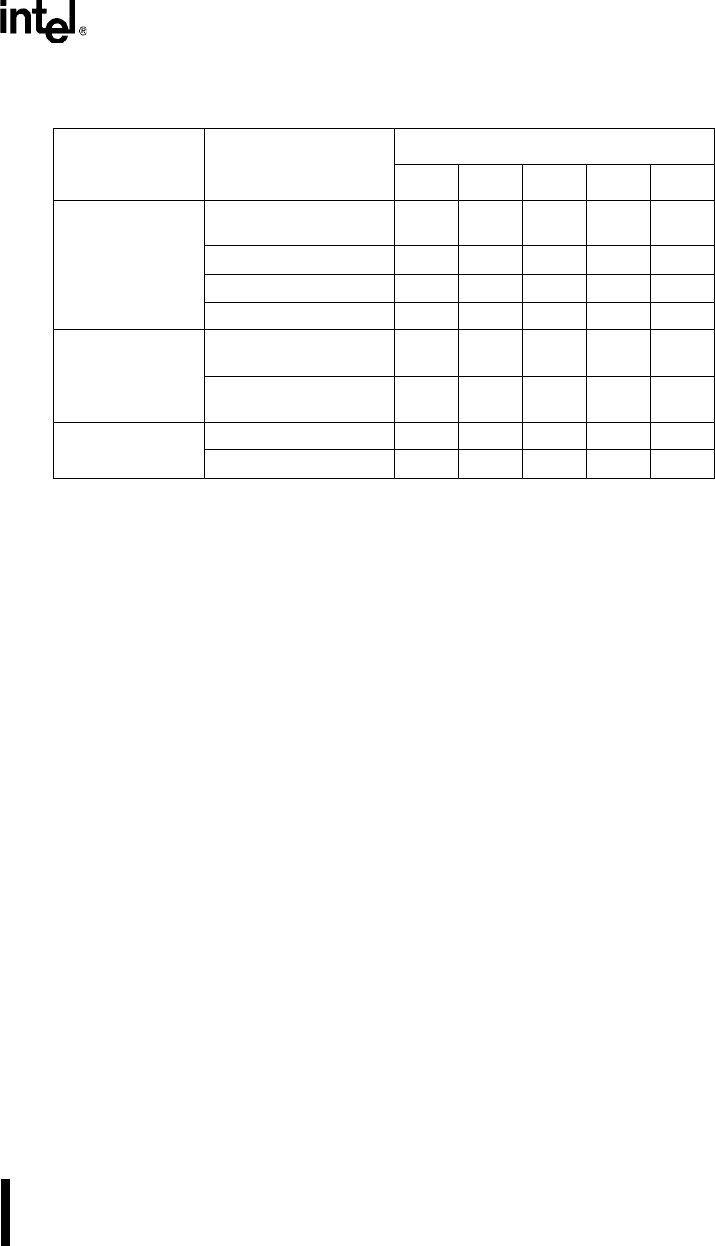

Table 5-10. The Effects of Instructions on the PSW and PSW1 Flags

Instruction Type Instruction

Flags Affected (1), (5)

CY OV AC (2) N Z

Arithmetic

ADD, ADDC, SUB,

SUBB, CMP

XXXXX

INC, DEC X X

MUL, DIV (3) 0 X X X

DA X X X

Logical

ANL, ORL, XRL, CLR A,

CPL A, RL, RR, SWAP

XX

RLC, RRC, SRL, SLL,

SRA (4)

XXX

Program Control

CJNE X X X

DJNE X X

NOTES:

1. X = the flag can be affected by the instruction.

0 = the flag is cleared by the instruction.

2. The AC flag is affected only by operations on 8-bit operands.

3. If the divisor is zero, the OV flag is set and the other bits are meaningless.

4. For SRL, SLL, and SRA instructions, the last bit shifted out is stored in the CY bit.

5. The parity bit (PSW.0) is set or cleared by instructions that change the contents of the

accumulator (ACC, Register R11).