A-5

INSTRUCTION SET REFERENCE

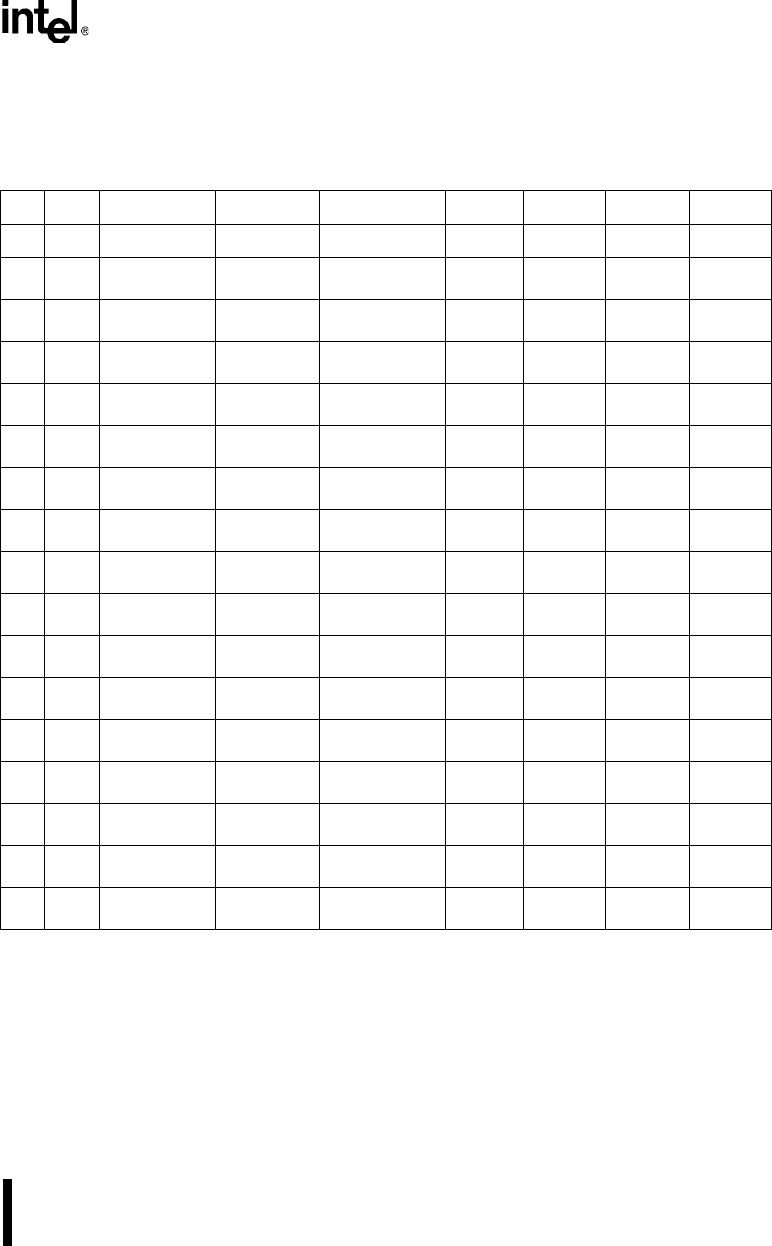

Table A-7. New Instructions for the MCS

®

251 Architecture

Bin. A5

x

8A5

x

9A5

x

AA5

x

BA5

x

CA5

x

DA5

x

EA5

x

F

Src.

x

8

x

9

x

A

x

B

x

C

x

D

x

E

x

F

0 JSLE

rel

MOV

Rm,@WRj+dis

MOVZ

WRj,Rm

INC R,#short (1)

MOV reg,ind

SRA

reg

1 JSG

rel

MOV

@WRj+dis,Rm

MOVS

WRj,Rm

DEC R,#short (1)

MOV ind,reg

SRL

reg

2JLE

rel

MOV

Rm,@DRk+dis

ADD

Rm,Rm

ADD

WRj,WRj

ADD

reg,op2 (2)

ADD

DRk,DRk

3JG

rel

MOV

@DRk+dis,Rm

SLL

reg

4 JSL

rel

MOV

WRj,@WRj+dis

ORL

Rm,Rm

ORL

WRj,WRj

ORL

reg,op2

(2)

5 JSGE

rel

MOV

@WRj+dis,WRj

ANL

Rm,Rm

ANL

WRj,WRj

ANL

reg,op2

(2)

6JE

rel

MOV

WRj,@DRk+dis

XRL

Rm,Rm

XRL

WRj,WRj

XRL

reg,op2

(2)

7 JNE

rel

MOV

@DRk+dis,WRj

MOV

op1,reg (2)

MOV

Rm,Rm

MOV

WRj,WRj

MOV

reg,op2

(2)

MOV

DRk,DRk

8 LJMP @WRj

EJMP @DRk

EJMP

addr24

DIV

Rm,Rm

DIV

WRj,WRj

9 LCALL@WRj

ECALL @DRk

ECALL

addr24

SUB

Rm,Rm

SUB

WRj,WRj

SUB

reg,op2

(2)

SUB

DRk,DRk

A Bit

Instructions (3)

ERET MUL

Rm,Rm

MUL

WRj,WRj

B TRAP CMP

Rm,Rm

CMP

WRj,WRj

CMP

reg,op2

(2)

CMP

DRk,DRk

C PUSH op1 (4)

MOV DRk,PC

D POP

op1

(4)

E

F

NOTES:

1. R = Rm/WRj/DRk.

2. op1, op2 are defined in Table A-8.

3. See Tables A-10 and A-11.

4. See Table A-12.