6-11

INTERRUPT SYSTEM

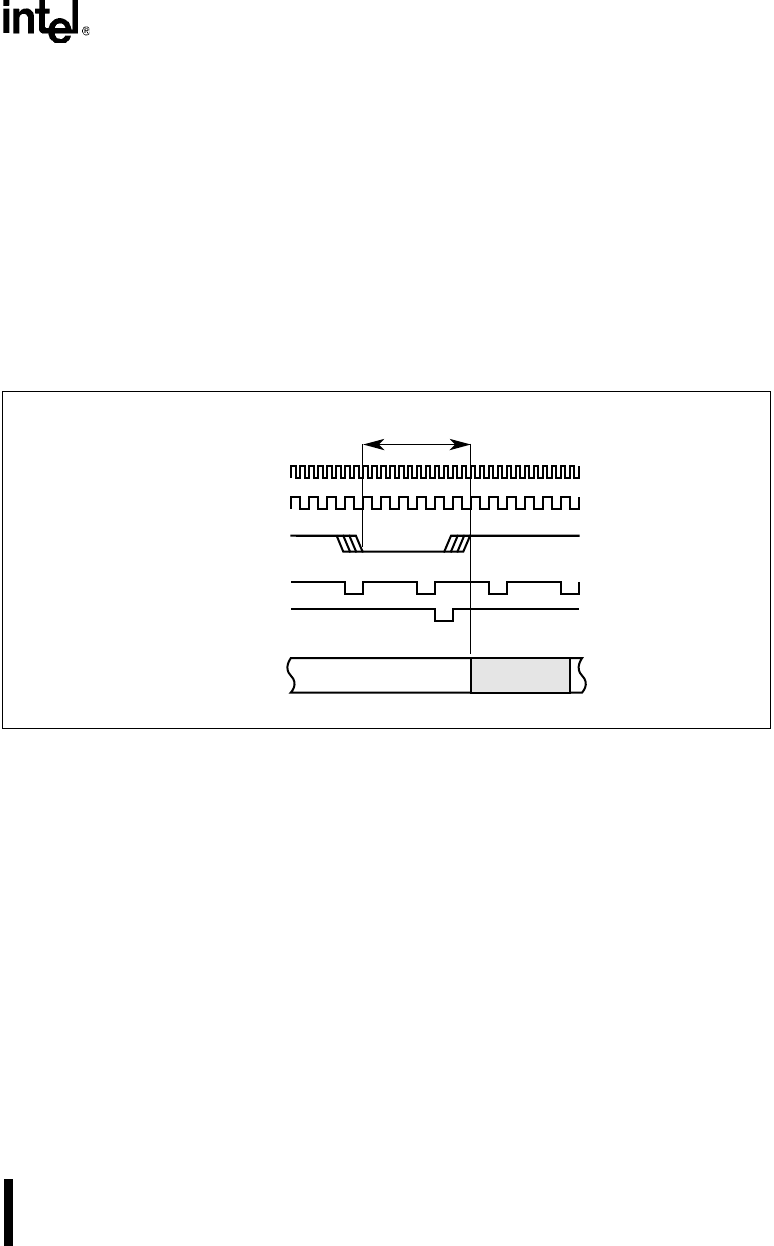

time is five states for internal interrupts and six states for external interrupts.

External interrupts must remain active for at least five state times to guarantee

interrupt recognition when the request occurs immediately after a sample has

been taken (i.e., requested in the second half of a sample state time).

If the external interrupt goes active one state after the sample state, the pin is not resampled for

another three states. After the second sample is taken and the interrupt request is recognized, the

interrupt controller requests the context switch. The programmer must also consider the time to

complete the instruction at the moment the context switch request is sent to the execution unit. If

9 states of a 10-state instruction have completed when the context switch is requested, the total

response time is 6 states, with a context switch immediately after the final state of the 10-state

instruction (see Figure 6-6).

Figure 6-6. Response Time Example #1

Conversely, if the external interrupt requests service in the state just prior to the next sample, re-

sponse is much quicker. One state asserts the request, one state samples, and one state requests

the context switch. If at that point the same instruction conditions exist, one additional state time

is needed to complete the 10-state instruction prior to the context switch (see Figure 6-7). The

total response time in this case is four state times. The programmer must evaluate all pertinent

conditions for accurate predictability.

OSC

State Time

INT0#

Sample INT0#

Response Time = 6

Ten State

Instruction

Request

Push PC

A4155-02