8XC251SA, SB, SP, SQ USER’S MANUAL

B-4

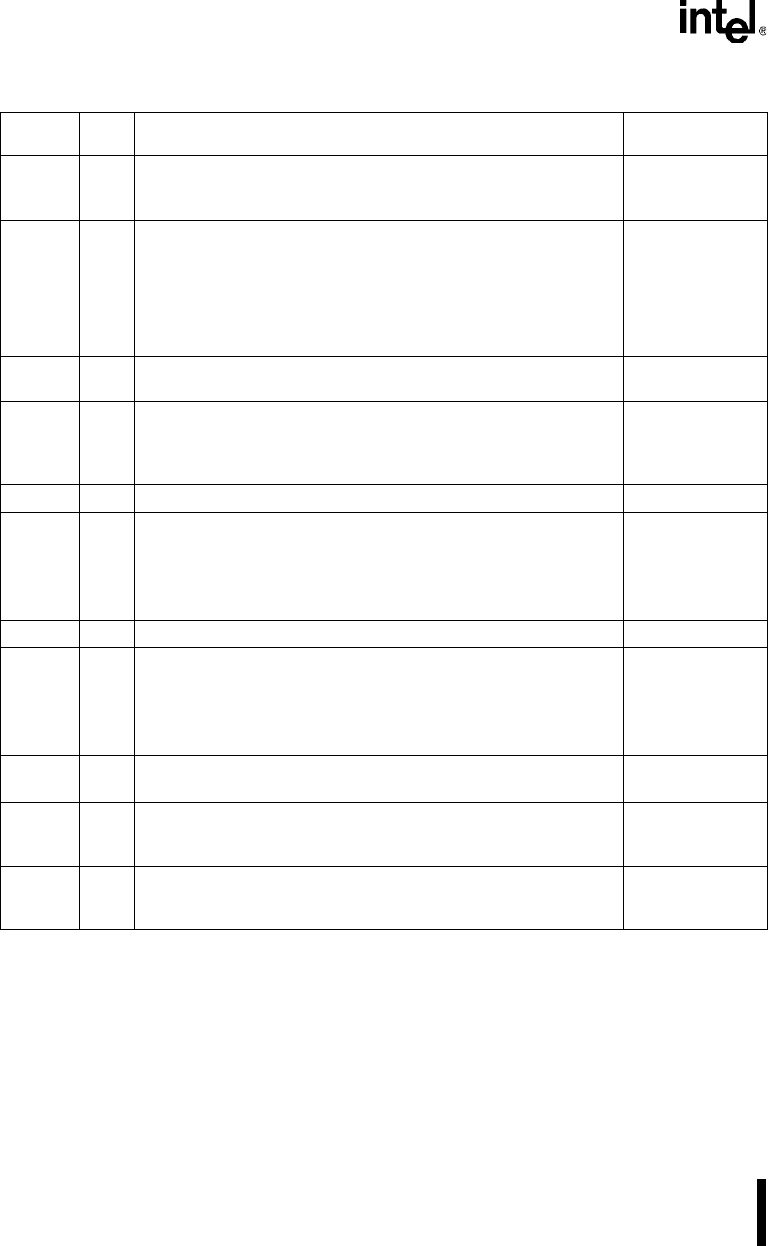

CEX2:0

CEX3

CEX4

I/O Programmable Counter Array (PCA) Input/Output Pins. These

are input signals for the PCA capture mode and output signals for

the PCA compare mode and PCA PWM mode.

P1.5:3

P1.6/WAIT#

P1.7/A17/WCLK

EA# I External Access. Directs program memory accesses to on-chip or

off-chip code memory. For EA# = 0, all program memory accesses

are off-chip. For EA# = 1, an access is to on-chip program memory

if the address is within the range of the on-chip program memory;

otherwise the access is off-chip. The value of EA# is latched at

reset. For devices without on-chip program memory, EA# must be

strapped to ground.

V

PP

ECI I PCA External Clock Input. External clock input to the 16-bit PCA

timer.

P1.2

INT1:0# I External Interrupts 0 and 1. These inputs set bits IE1:0 in the

TCON register. If bits IT1:0 in the TCON register are set, bits IE1:0

are set by a falling edge on INT1#/INT0#. If bits INT1:0 are clear,

bits IE1:0 are set by a low level on INT1:0#.

P3.3:2

P0.7:0 I/O Port 0. This is an 8-bit, open-drain, bidirectional I/O port. AD7:0

P1.0

P1.1

P1.2

P1.5:3

P1.6

P1.7

I/O Port 1. This is an 8-bit, bidirectional I/O port with internal pullups. T2

T2EX

ECI

CEX2:0

CEX3/WAIT#

CEX4/A17/WCLK

P2.7:0 I/O Port 2. This is an 8-bit, bidirectional I/O port with internal pullups. A15:8

P3.0

P3.1

P3.3:2

P3.5:4

P3.6

P3.7

I/O Port 3. This is an 8-bit, bidirectional I/O port with internal pullups. RXD

TXD

INT1:0#

T1:0

WR#

RD#/A16

PROG# I Programming Pulse. The programming pulse is applied to this pin

for programming the on-chip nonvolatile memory.

ALE

PSEN# O Program Store Enable. Read signal output to external memory.

Asserted for the address range specified by configuration byte

UCONFIG0, bits RD1:0 (Table B-3). Also see RD#.

—

RD# O Read. Read signal output to external data memory. Asserted for

the address range specified by configuration byte UCONFIG0, bits

RD1:0 (Table B-3). Also see PSEN# and A16.

P3.7/A16

Table B-2. Signal Descriptions (Continued)

Signal

Name

Type Description

Alternate

Function

†

The descriptions of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the nonpage mode chip configuration (com-

patible with 44-pin PLCC and 40-pin DIP MCS

®

51 microcontrollers). If the chip is configured for page

mode operation, port 0 carries the lower address bits (A7:0), and port 2 carries the upper address bits

(A15:8) and the data (D7:0).