4-7

DEVICE CONFIGURATION

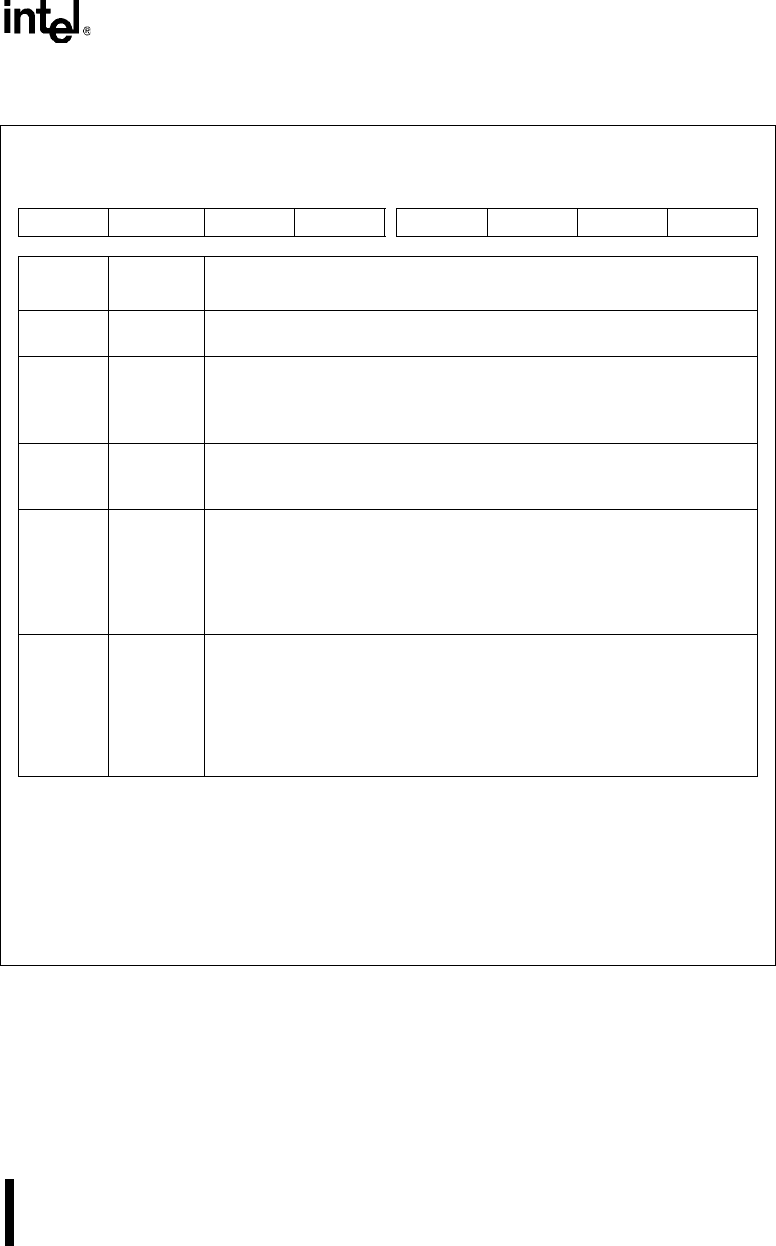

Figure 4-4. Configuration Byte UCONFIG1

UCONFIG1

(1), (3)

Address:FF:FFF9H (2)

7 0

— — — INTR WSB WSB1# WSB0# EMAP#

Bit

Number

Bit

Mnemonic

Function

7:5 — Reserved for internal or future use. Set these bits when programming

UCONFIG1.

4 INTR Interrupt Mode:

If this bit is set, interrupts push 4 bytes onto the stack (the 3 bytes of the PC

and PSW1). If this bit is clear, interrupts push the 2 lower bytes of the PC

onto the stack. See 4.8, “Interrupt Mode (INTR).”

3 WSB Wait State B. Use only for A-step compatibility:

Clear this bit to generate one external wait state for memory region 01:. Set

this bit for no wait states for region 01:.

2:1 WSB1:0# External Wait State B (Region 01:):

WSB1# WSB0#

0 0 Inserts 3 wait states for region 01:

0 1 Inserts 2 wait states for region 01:

1 0 Inserts 1 wait state for region 01:

1 1 Zero wait states for region 01:

0 EMAP# EPROM Map:

For devices with 16 Kbytes of on-chip code memory, clear this bit to map the

upper half of on-chip code memory to region 00: (data memory). Maps

FF:2000H–FF:3FFFH to 00:E000H–00:FFFFH. If this bit is set, mapping

does not occur and addresses in the range 00:E000H–00:FFFFH

access

external RAM. See 4.7, “Mapping On-chip Code Memory to Data Memory

(EMAP#).”

NOTES:

1. User configuration bytes UCONFIG0 and UCONFIG1 define the configuration of the 8XC251S

x

.

2. Address. UCONFIG1 is the second-lowest byte of the 8-byte configuration array. As determined by

UCON and EA#, the 8XC251SA, SB, SP, SQ fetches configuration information from on-chip nonvolatile

memory at addresses FF:FFF8H and FF:FFF9H or from external memory using these same

addresses. In external memory, configuration information is obtained from an 8-byte configuration

array located at the highest addresses implemented. The physical location of the configuration array in

external memory depends on the size and decode arrangement of the external memory (Table 4-1 and

Figure 4-2).

3. Instructions for programming and verifying on-chip configuration bytes are given in Chapter 14.