A-23

INSTRUCTION SET REFERENCE

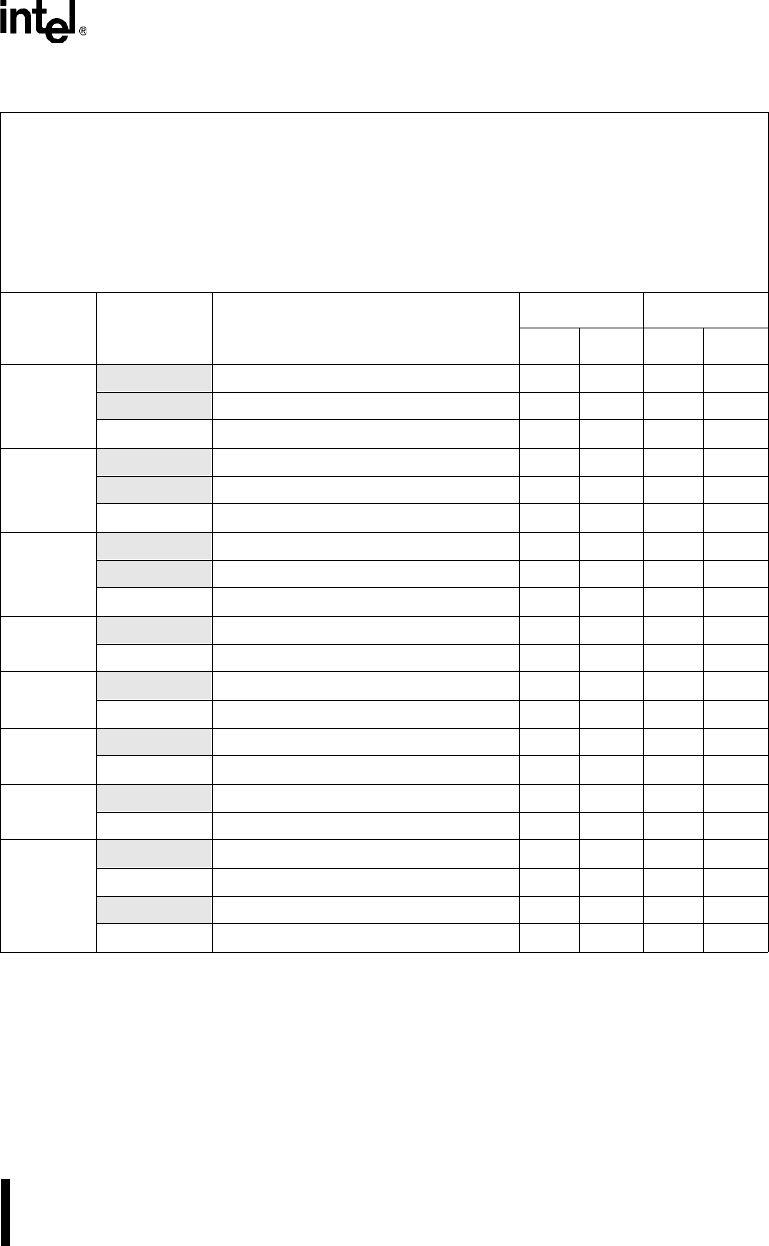

Table A-26. Summary of Bit Instructions

Clear Bit CLR bit bit ← 0

Set Bit SETB bit bit ← 1

Complement Bit CPL bit bit← Øbit

AND Carry with Bit ANL CY,bit CY ← CY Λ bit

AND Carry with Complement of Bit ANL CY,/bit CY ← CY Λ Øbit

OR Carry with Bit ORL CY,bit CY ← CY V bit

ORL Carry with Complement of Bit ORL CY,/bit CY ← CY V Øbit

Move Bit to Carry MOV CY,bit CY ← bit

Move Bit from Carry MOV bit,CY bit ← CY

Mnemonic <src>,<dest> Notes

Binary Mode Source Mode

Bytes States Bytes States

CLR

CY Clear carry 1 1 1 1

bit51 Clear dir bit 2 2 (2) 2 2 (2)

bit Clear dir bit 4 4 3 3

SETB

CY Set carry 1 1 1 1

bit51 Set dir bit 2 2 (2) 2 2 (2)

bit Set dir bit 4 4 (2) 3 3 (2)

CPL

CY Complement carry 1 1 1 1

bit51 Complement dir bit 2 2 (2) 2 2 (2)

bit Complement dir bit 4 4 (2) 3 3 (2)

ANL

CY,bit51 AND dir bit to carry 2 1 (3) 2 1 (3)

CY,bit AND dir bit to carry 4 3 (3) 3 2 (3)

ANL/

CY,/bit51 AND complemented dir bit to carry 2 1 (3) 2 1 (3)

CY,/bit AND complemented dir bit to carry 4 3 (3) 3 2 (3)

ORL

CY,bit51 OR dir bit to carry 2 1 (3) 2 1 (3)

CY,bit OR dir bit to carry 4 3 (3) 3 2 (3)

ORL/

CY,/bit51 OR complemented dir bit to carry 2 1 (3) 2 1 (3)

CY,/bit OR complemented dir bit to carry 4 3 (3) 3 2 (3)

MOV

CY,bit51 Move dir bit to carry 2 1 (3) 2 1 (3)

CY,bit Move dir bit to carry 4 3 (3) 3 2 (3)

bit51,CY Move carry to dir bit 2 2 (2) 2 2 (2)

bit,CY Move carry to dir bit 4 4 (2) 3 3 (2)

NOTES:

1. A shaded cell denotes an instruction in the MCS

®

51 architecture.

2. If this instruction addresses an I/O port (P

x

,

x

= 0–3), add 2 to the number of states.

3. If this instruction addresses an I/O port (P

x

,

x

= 0–3), add 1 to the number of states.