8XC251SA, SB, SP, SQ USER’S MANUAL

C-14

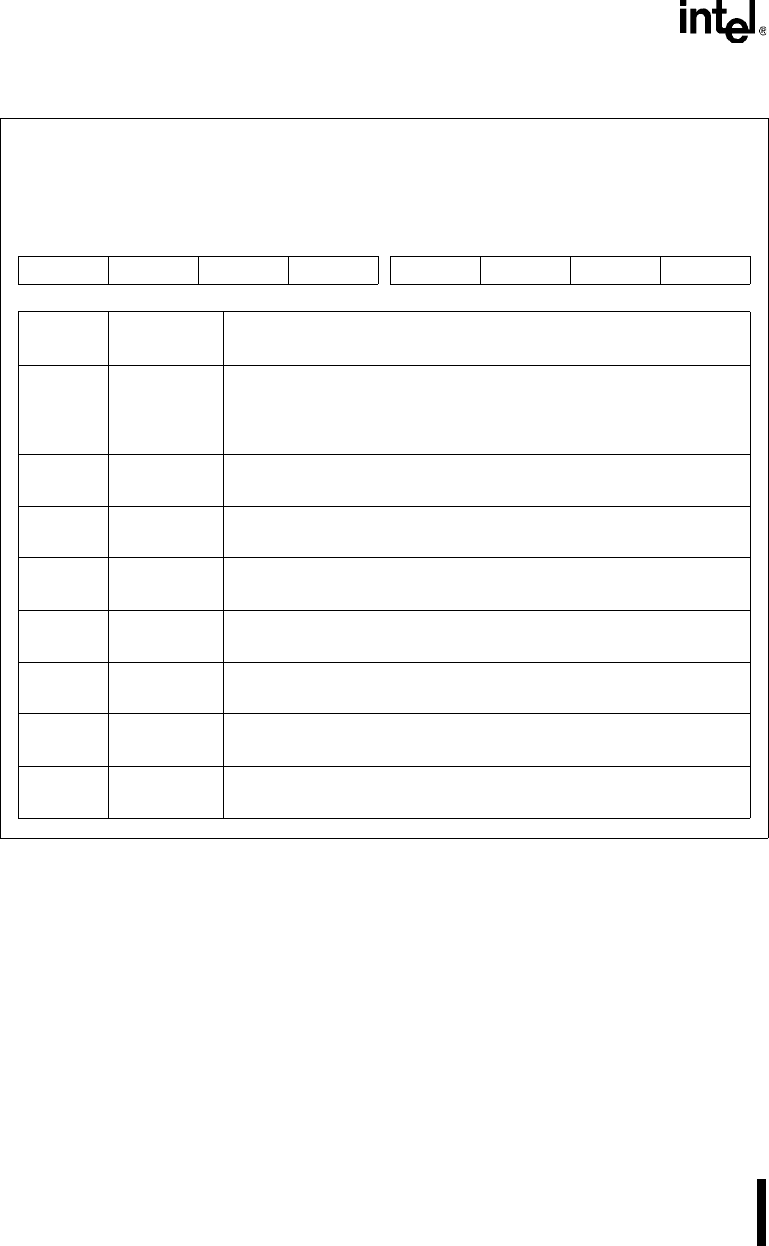

IE0

Address: S:A8H

Reset State: 0000 0000B

Interrupt Enable Register 0. IE0 contains two types of interrupt enable bits. The global enable bit (EA)

enables/disables all of the interrupts, except the TRAP interrupt, which is always enabled. The

remaining bits enable/disable the other individual interrupts.

7 0

EA EC ET2 ES ET1 EX1 ET0 EX0

Bit

Number

Bit

Mnemonic

Function

7 EA Global Interrupt Enable:

Setting this bit enables all interrupts that are individually enabled by bits

0–6. Clearing this bit disables all interrupts, except the TRAP interrupt,

which is always enabled.

6 EC PCA Interrupt Enable:

Setting this bit enables the PCA interrupt.

5 ET2 Timer 2 Overflow Interrupt Enable:

Setting this bit enables the timer 2 overflow interrupt.

4 ES Serial I/O Port Interrupt Enable:

Setting this bit enables the serial I/O port interrupt.

3 ET1 Timer 1 Overflow Interrupt Enable:

Setting this bit enables the timer 1 overflow interrupt.

2 EX1 External Interrupt 1 Enable:

Setting this bit enables external interrupt 1.

1 ET0 Timer 0 Overflow Interrupt Enable:

Setting this bit enables the timer 0 overflow interrupt.

0 EX0 External Interrupt 0 Enable:

Setting this bit enables external interrupt 0.