5-3

PROGRAMMING

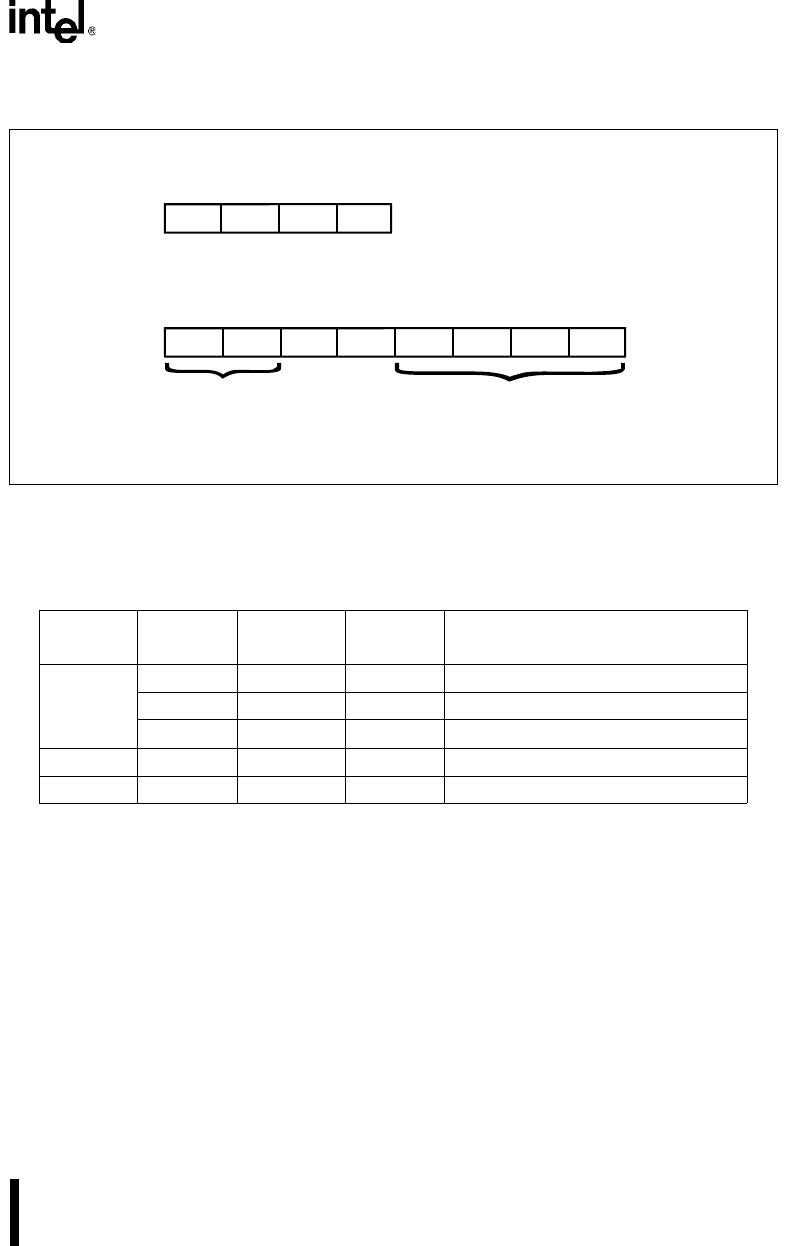

Figure 5-1. Word and Double-word Storage in Big Endien Form

Instructions in the MCS 51 architecture use 80H–FFH as addresses for both memory locations

and SFRs, because memory locations are addressed only indirectly and SFR locations are ad-

dressed only directly. For compatibility, software tools for MCS 251 controllers recognize this

notation for instructions in the MCS 51 architecture. No change is necessary in any code written

for MCS 51 controllers.

For new instructions in the MCS 251 architecture, the memory region prefixes (00:, 01, ..., FF:)

and the SFR prefix (S:) are required. Also, software tools for the MCS 251 architecture permit

00: to be used for memory addresses 00H–FFH and permit the prefix S: to be used for SFR ad-

dresses in instructions in the MCS 51 architecture.

Table 5-2. Notation for Byte Registers, Word Registers, and Dword Registers

Register

Type

Register

Symbol

Destination

Register

Source

Register

Register Range

Byte

Ri — — R0, R1

Rn — — R0–R7

Rm Rmd Rms R0–R15

Word WRj WRjd WRjs WR0, WR2, WR4, ..., WR30

Dword DRk DRkd DRks DR0, DR4, DR8, ..., DR28, DR56, DR60

MOV WR0,#A3B6H

MOV 00:0201H,WR0

MOV DR4,#0000C4D7H

A3H

B6H

2

3

WR0

4

5

6

0

1

7

00H 00H

C4H

D7H

DR4

Register File

Memory

Contents of register file and memory after execution

A4242-01

200H

201H

202H

203H

A3H

B6H