A-3

INSTRUCTION SET REFERENCE

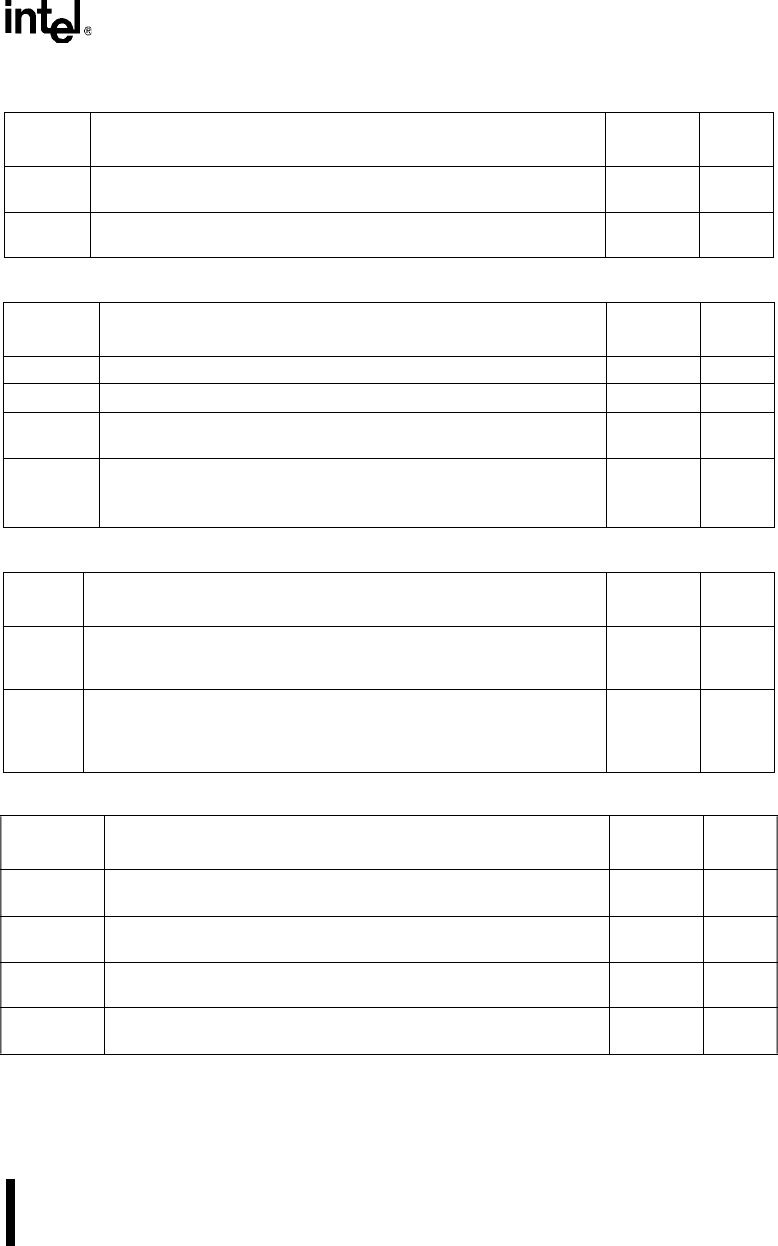

Table A-2. Notation for Direct Addresses

Direct

Address.

Description

MCS

®

251

Arch.

MCS 51

Arch.

dir8 An 8-bit direct address. This can be a memory address

(00:0000H–00:00FFH) or an SFR address (S:00H - S:FFH).

✔✔

dir16 A 16-bit memory address (00:0000H–00:FFFFH) used in direct

addressing.

✔

Table A-3. Notation for Immediate Addressing

Immediate

Data

Description

MCS

®

251

Arch.

MCS 51

Arch.

#data An 8-bit constant that is immediately addressed in an instruction. ✔✔

#data16 A 16-bit constant that is immediately addressed in an instruction. ✔

#0data16

#1data16

A 32-bit constant that is immediately addressed in an instruction. The

upper word is filled with zeros (#0data16) or ones (#1data16).

✔

#short

v v

A constant, equal to 1, 2, or 4, that is immediately addressed in an

instruction.

Binary representation of #short.

✔

Table A-4. Notation for Bit Addressing

Bit

Address

Description

MCS

®

251

Arch.

MCS 51

Arch.

bit

y y y

A directly addressed bit in memory locations 00:0020H–00:007FH or in

any defined SFR.

A binary representation of the bit number (0–7) within a byte.

✔

bit51 A directly addressed bit (bit number = 00H–FFH) in memory or an SFR.

Bits 00H–7FH are the 128 bits in byte locations 20H–2FH in the on-chip

RAM. Bits 80H–FFH are the 128 bits in the 16 SFR’s with addresses

that end in 0H or 8H: S:80H, S:88H, S:90H, . . . , S:F0H, S:F8H.

✔

Table A-5. Notation for Destinations in Control Instructions

Destination

Address

Description

MCS

®

251

Arch.

MCS 51

Arch.

rel A signed (two's complement) 8-bit relative address. The destination is

-128 to +127 bytes relative to first byte of the next instruction.

✔✔

addr11 An 11-bit destination address. The destination is in the same 2-Kbyte

block of memory as the first byte of the next instruction.

✔✔

addr16 A 16-bit destination address. A destination can be anywhere within

the same 64-Kbyte region as the first byte of the next instruction.

✔✔

addr24 A 24-bit destination address. A destination can be anywhere within

the 16-Mbyte address space.

✔