C-27

REGISTERS

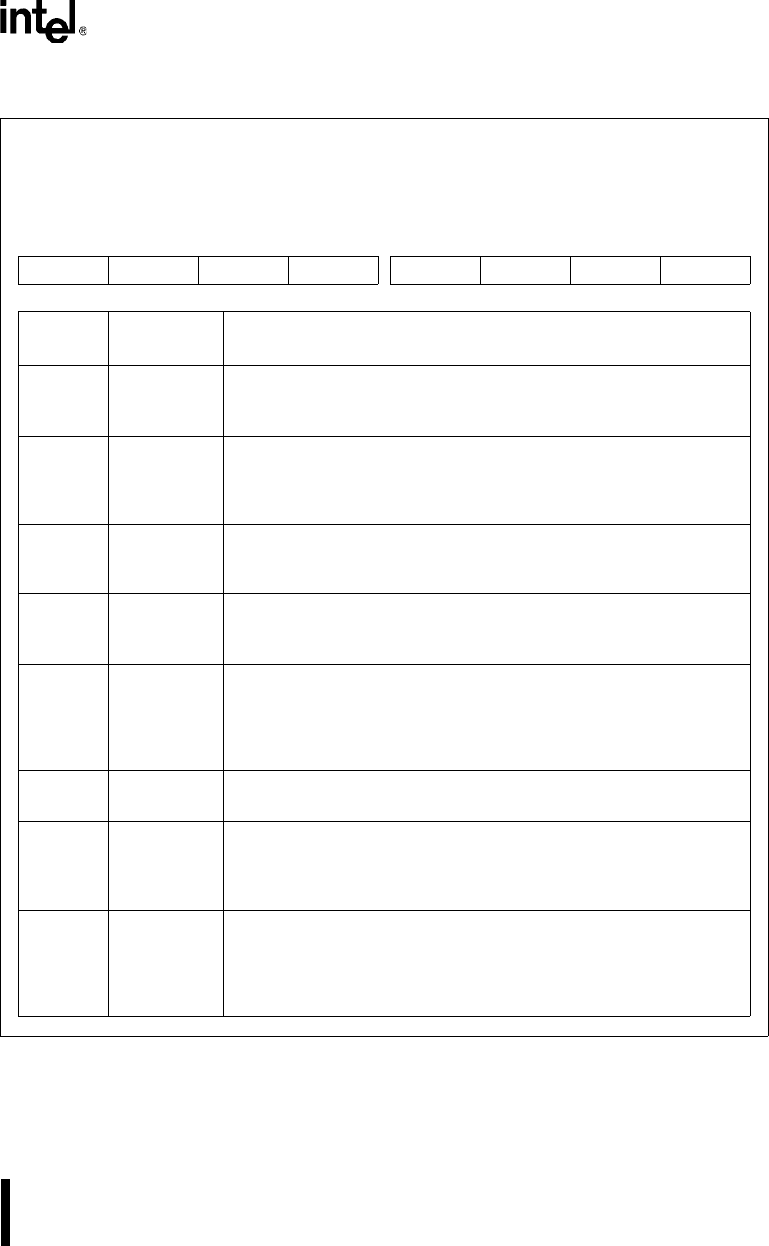

T2CON

Address: S:C8H

Reset State: 0000 0000B

Timer 2 Control Register. Contains the receive clock, transmit clock, and capture/reload bits used to

configure timer 2. Also contains the run control bit, counter/timer select bit, overflow flag, external flag,

and external enable for timer 2.

7 0

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#

Bit

Number

Bit

Mnemonic

Function

7 TF2 Timer 2 Overflow Flag:

Set by timer 2 overflow. Must be cleared by software. TF2 is not set if

RCLK = 1 or TCLK = 1.

6 EXF2 Timer 2 External Flag:

If EXEN2 = 1, capture or reload caused by a negative transition on T2EX

sets EFX2. EXF2 does not cause an interrupt in up/down counter mode

(DCEN = 1).

5 RCLK Receive Clock Bit:

Selects timer 2 overflow pulses (RCLK = 1) or timer 1 overflow pulses

(RCLK = 0) as the baud rate generator for serial port modes 1 and 3.

4 TCLK Transmit Clock Bit:

Selects timer 2 overflow pulses (TCLK = 1) or timer 1 overflow pulses

(TCLK = 0) as the baud rate generator for serial port modes 1 and 3.

3 EXEN2 Timer 2 External Enable Bit:

Setting EXEN2 causes a capture or reload to occur as a result of a

negative transition on T2EX unless timer 2 is being used as the baud

rate generator for the serial port. Clearing EXEN2 causes timer 2 to

ignore events at T2EX.

2 TR2 Timer 2 Run Control Bit:

Setting this bit starts the timer.

1 C/T2# Timer 2 Counter/Timer Select:

C/T2# = 0 selects timer operation: timer 2 counts the divided-down

system clock. C/T2# = 1 selects counter operation: timer 2 counts

negative transitions on external pin T2.

0 CP/RL2# Capture/Reload Bit:

When set, captures occur on negative transitions at T2EX if EXEN2 = 1.

When cleared, auto-reloads occur on timer 2 overflows or negative

transitions at T2EX if EXEN2 = 1. The CP/RL2# bit is ignored and timer 2

forced to auto-reload on timer 2 overflow, if RCLK = 1 or TCLK = 1.