8XC251SA, SB, SP, SQ USER’S MANUAL

6-4

6.2.2 Timer Interrupts

Two timer-interrupt request bits TF0 and TF1 (see TCON register, Figure 8-6 on page 8-8) are set

by timer overflow (the exception is Timer 0 in Mode 3, see Figure 8-4 on page 8-6). When a timer

interrupt is generated, the bit is cleared by an on-chip hardware vector to an interrupt service rou-

tine. Timer interrupts are enabled by bits ET0, ET1, and ET2 in the IE0 register (see Figure 6-2,

"Interrupt Enable Register”).

Timer 2 interrupts are generated by a logical OR of bits TF2 and EXF2 in register T2CON (see

Figure 8-12 on page 8-17). Neither flag is cleared by a hardware vector to a service routine. In

fact, the interrupt service routine must determine if TF2 or EXF2 generated the interrupt, and then

clear the bit. Timer 2 interrupt is enabled by ET2 in register IE0.

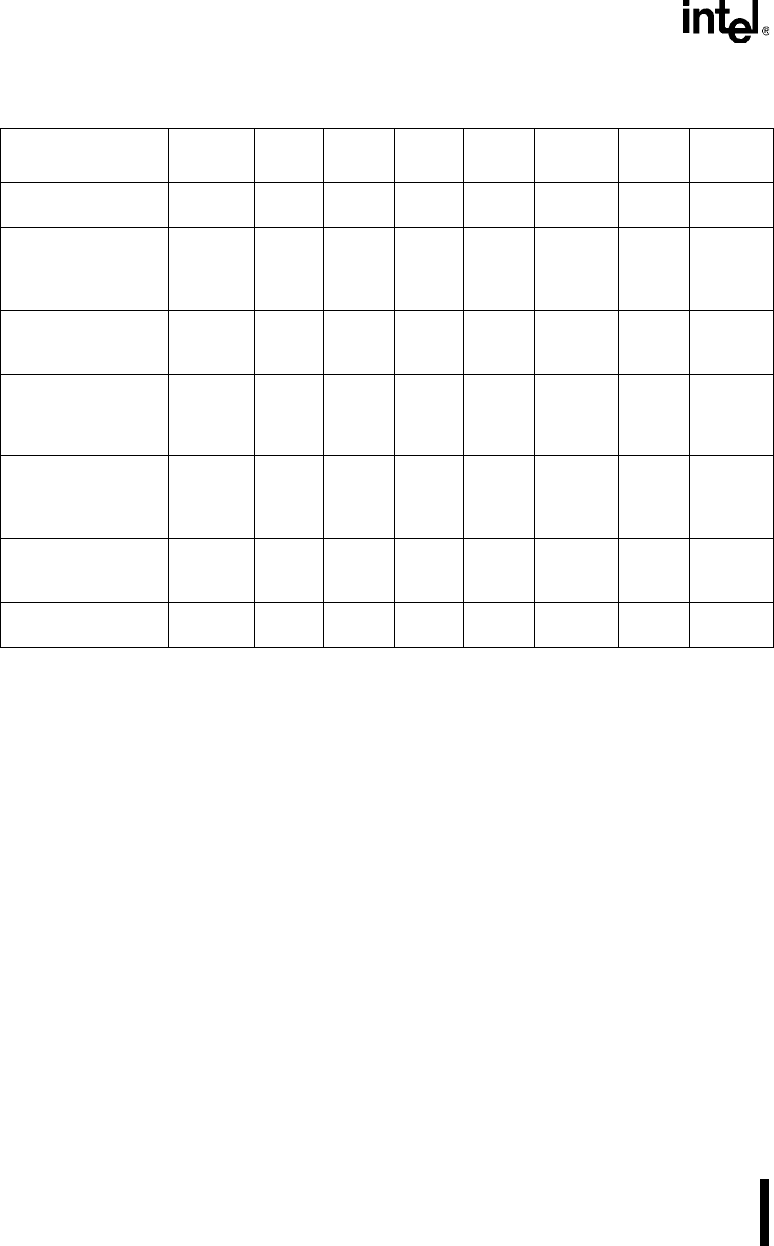

Table 6-3. Interrupt Control Matrix

Interrupt Name

Global

Enable

PCA

Timer

2

Serial

Port

Timer

1

INT1#

Timer

0

INT0#

Bit Name in IE0

Register

EA EC ET2 ES ET1 EX1 ET0 EX0

Interrupt Priority-

Within-Level

(7 = Low Priority,

1 = High Priority)

NA7654 3 2 1

Bit Names in:

IPH0

IPL0

Reserved

Reserved

IPH0.6

IPL0.6

IPH0.5

IPL0.5

IPH0.4

IPL0.4

IPH0.3

IPL0.3

IPH0.2

IPL0.2

IPH0.1

IPL0.1

IPH0.0

IPL0.0

Programmable for

Negative-edge

Triggered or Level-

triggered Detect?

NA Edge No No No Yes No Yes

Interrupt Request

Flag in CCON,

T2CON, SCON, or

TCON Register

NA

CF,

CCF

x

TF2,

EXF2

RI, TI TF1 IE1 TF0 IE0

Interrupt Request

Flag Cleared by

Hardware?

No No No No Yes

Edge

Yes,

Level No

Yes

Edge

Yes,

Level No

ISR Vector Address

NA

FF:

0033H

FF:

002BH

FF:

0023H

FF:

001BH

FF:

0013H

FF:

000BH

FF:

0003H