10-3

SERIAL I/O PORT

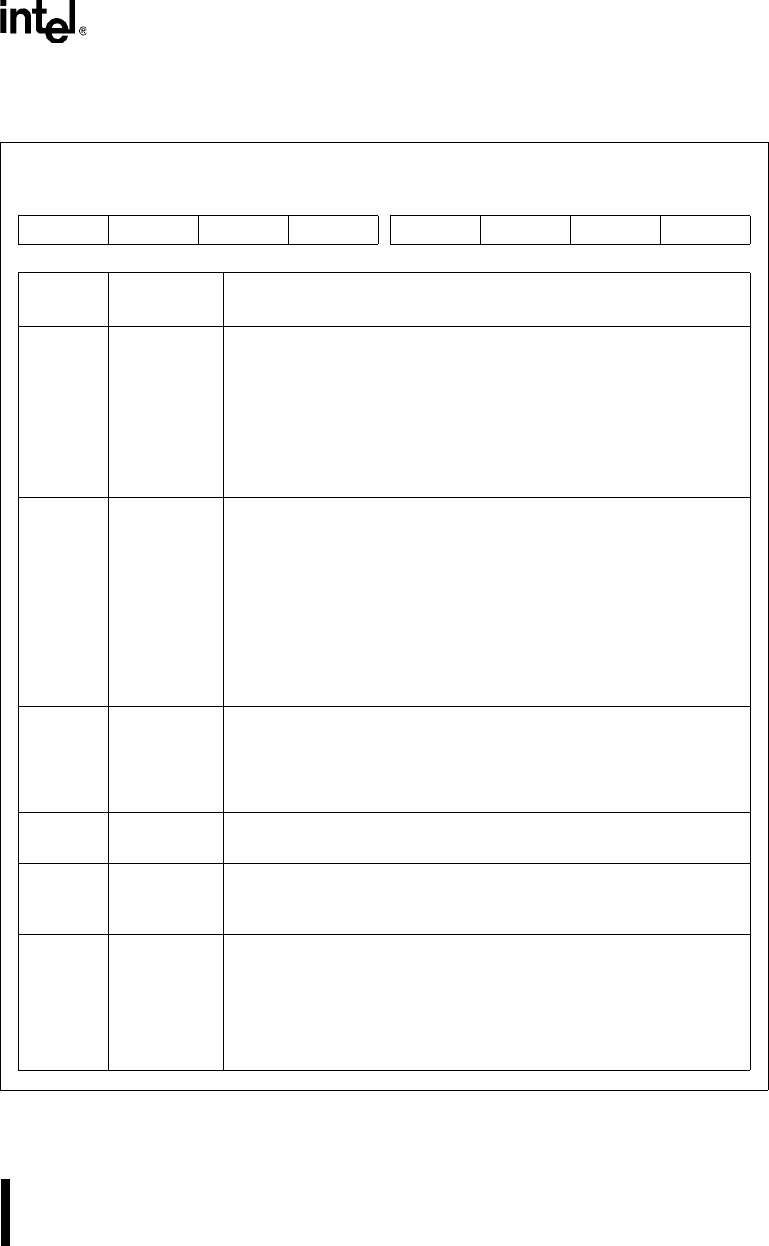

The serial port control (SCON) register (Figure 10-2) configures and controls the serial port.

Figure 10-2. SCON: Serial Port Control Register

SCON

Address: 98H

Reset State: 0000 0000B

7 0

FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

Bit

Number

Bit

Mnemonic

Function

7FE

SM0

Framing Error Bit:

To select this function, set the SMOD0 bit in the PCON register. Set by

hardware to indicate an invalid stop bit. Cleared by software, not by valid

frames.

Serial Port Mode Bit 0:

To select this function, clear the SMOD0 bit in the PCON register.

Software writes to bits SM0 and SM1 to select the serial port operating

mode. Refer to the SM1 bit for the mode selections.

6 SM1 Serial Port Mode Bit 1:

Software writes to bits SM1 and SM0 (above) to select the serial port

operating mode.

SM0 SM1 Mode Description Baud Rate

0 0 0 Shift register F

OSC

/12

0 1 1 8-bit UART Variable

1 0 2 9-bit UART F

OSC

/32

†

or F

OSC

/64

†

1 1 3 9-bit UART Variable

†

Select by programming the SMOD bit in the PCON register (see section

10.6, “Baud Rates”).

5 SM2 Serial Port Mode Bit 2:

Software writes to bit SM2 to enable and disable the multiprocessor

communication and automatic address recognition features. This allows

the serial port to differentiate between data and command frames and to

recognize slave and broadcast addresses.

4 REN Receiver Enable Bit:

To enable reception, set this bit. To enable transmission, clear this bit.

3 TB8 Transmit Bit 8:

In modes 2 and 3, software writes the ninth data bit to be transmitted to

TB8. Not used in modes 0 and 1.

2 RB8 Receiver Bit 8:

Mode 0: Not used.

Mode 1 (SM2 clear): Set or cleared by hardware to reflect the stop bit

received.

Modes 2 and 3 (SM2 set): Set or cleared by hardware to reflect the ninth

data bit received.