6-7

INTERRUPT SYSTEM

6.6 INTERRUPT PRIORITIES

Each of the seven 8XC251Sx interrupt sources may be individually programmed to one of four

priority levels. This is accomplished with the IPH0.x/IPL0.x bit pairs in the interrupt priority high

(IPH0) and interrupt priority low (IPL0) registers (Figures 6-3 and 6-4 on page 6-8). Specify the

priority level as shown in Table 6-4 using IPH0.x as the MSB and IPL0.x as the LSB.

A low-priority interrupt is always interrupted by a higher priority interrupt but not by another in-

terrupt of equal or lower priority. The highest priority interrupt is not interrupted by any other in-

terrupt source. Higher priority interrupts are serviced before lower priority interrupts. The

response to simultaneous occurrence of equal priority interrupts (i.e., sampled within the same

four state interrupt cycle) is determined by a hardware priority-within-level resolver (see Table

6-5).

NOTE

The 8XC251Sx Interrupt Priority Within Level table (Table 6-5) differs from

MCS

®

51 microcontrollers. Other MCS

251 microcontrollers may have unique

interrupt priority within level tables.

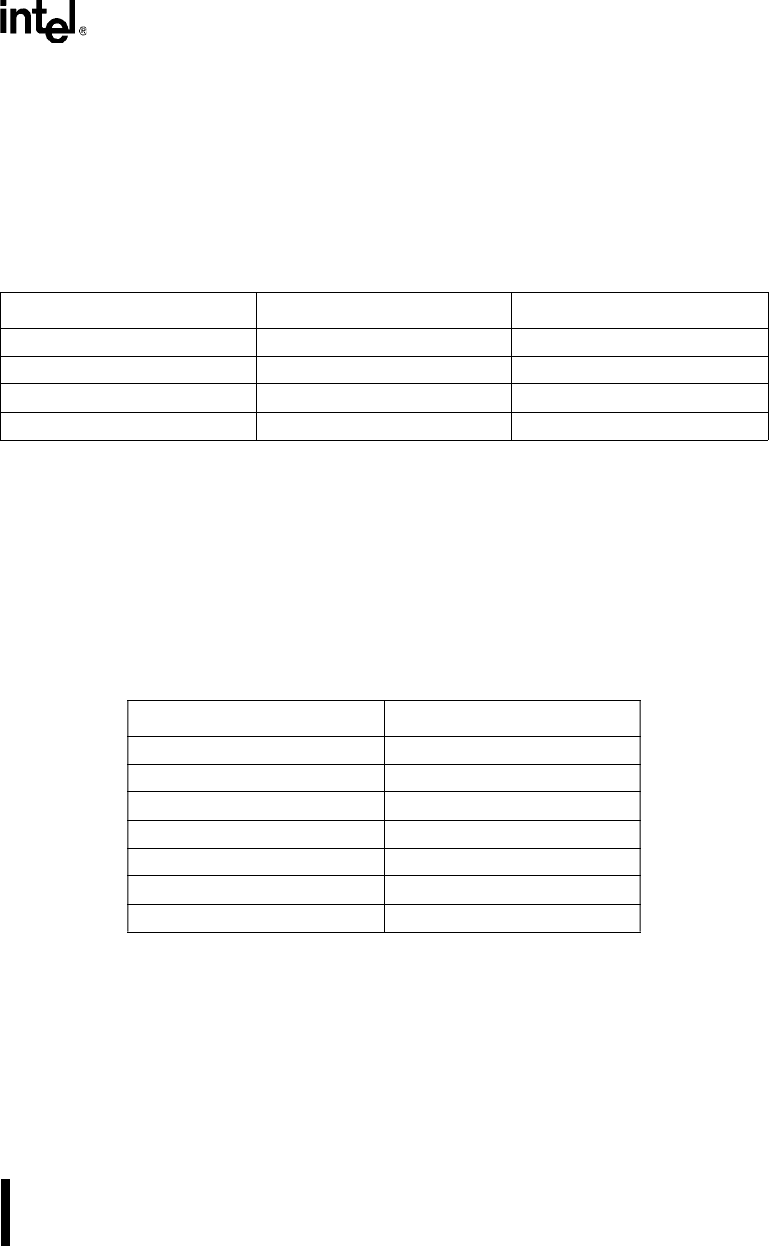

Table 6-4. Level of Priority

IPH0.

x

(MSB) IPL0.

x

(LSB) Priority Level

0 0 0 Lowest Priority

011

102

1 1 3 Highest Priority

Table 6-5. Interrupt Priority Within Level

Priority Number Interrupt Name

1 (Highest Priority) INT0#

2 Timer 0

3INT1#

4 Timer 1

5 Serial Port

6 Timer 2

7 (Lowest Priority) PCA