8XC251SA, SB, SP, SQ USER’S MANUAL

14-8

14.6.4 Encryption Array

The 87C251Sx and 83C251Sx controllers include a 128-byte encryption array located in nonvol-

atile memory outside the memory address space. During verification of the on-chip code memory,

the seven low-order address bits also address the encryption array. As the byte of the code mem-

ory is read, it is exclusive-NOR’ed (XNOR) with the key byte from the encryption array. If the

encryption array is not programmed (still all 1s), the user program code is placed on the data bus

in its original, unencrypted form. If the encryption array is programmed with key bytes, the user

program code is encrypted and can’t be used without knowledge of the key byte sequence.

CAUTION

If the encryption feature is implemented, the portion of the on-chip code

memory that does not contain program code should be filled with “random”

byte values other than FFH to prevent the encryption key sequence from being

revealed.

To program the encryption array, perform the procedure described in section 14.4, “Programming

Algorithm,” using the program encryption array mode (Table 14-1).

To preserve the secrecy of the encryption key byte sequence, the encryption array can not be ver-

ified.

14.6.5 Signature Bytes

The 87C251Sx and 83C251Sx contain factory-programmed signature bytes. These bytes are lo-

cated in nonvolatile memory outside the memory address space at 30H, 31H, 60H, and 61H. To

read the signature bytes, perform the procedure described in 14.5, “Verify Algorithm,” using the

verify signature mode (Table 14-1). Signature byte values are listed in Table 14-3.

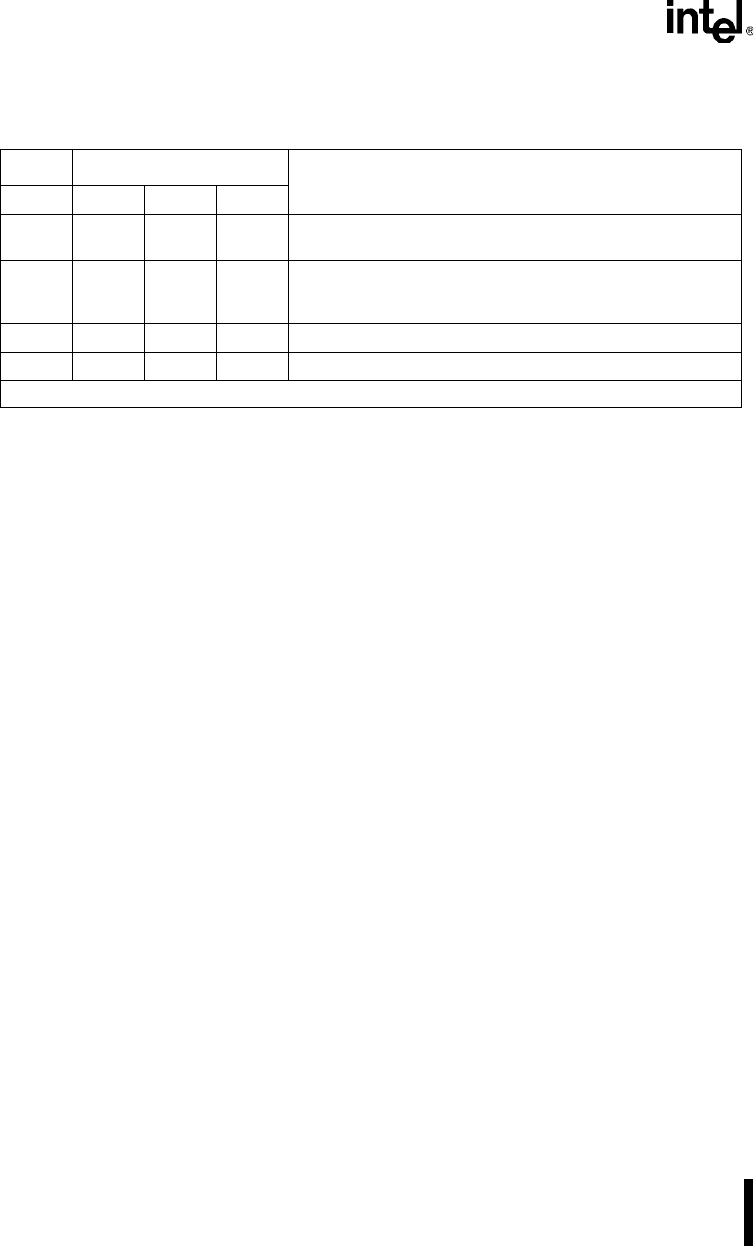

Table 14-2. Lock Bit Function

Lock Bits Programmed Protection Type

LB3 LB2 LB1

Level 1 U U U No program lock features are enabled. On-chip user code is

encrypted when verified, if encryption array is programmed.

Level 2 U U P External code is prevented from fetching code bytes from on-

chip code memory. Further programming of the on-chip

OTPROM is disabled.

Level 3 U P P Same as level 2, plus on-chip code memory verify is disabled.

Level 4 P P P Same as level 3, plus external memory execution is disabled.

NOTE: Other combinations of the lock bits are not defined.