13-5

EXTERNAL MEMORY INTERFACE

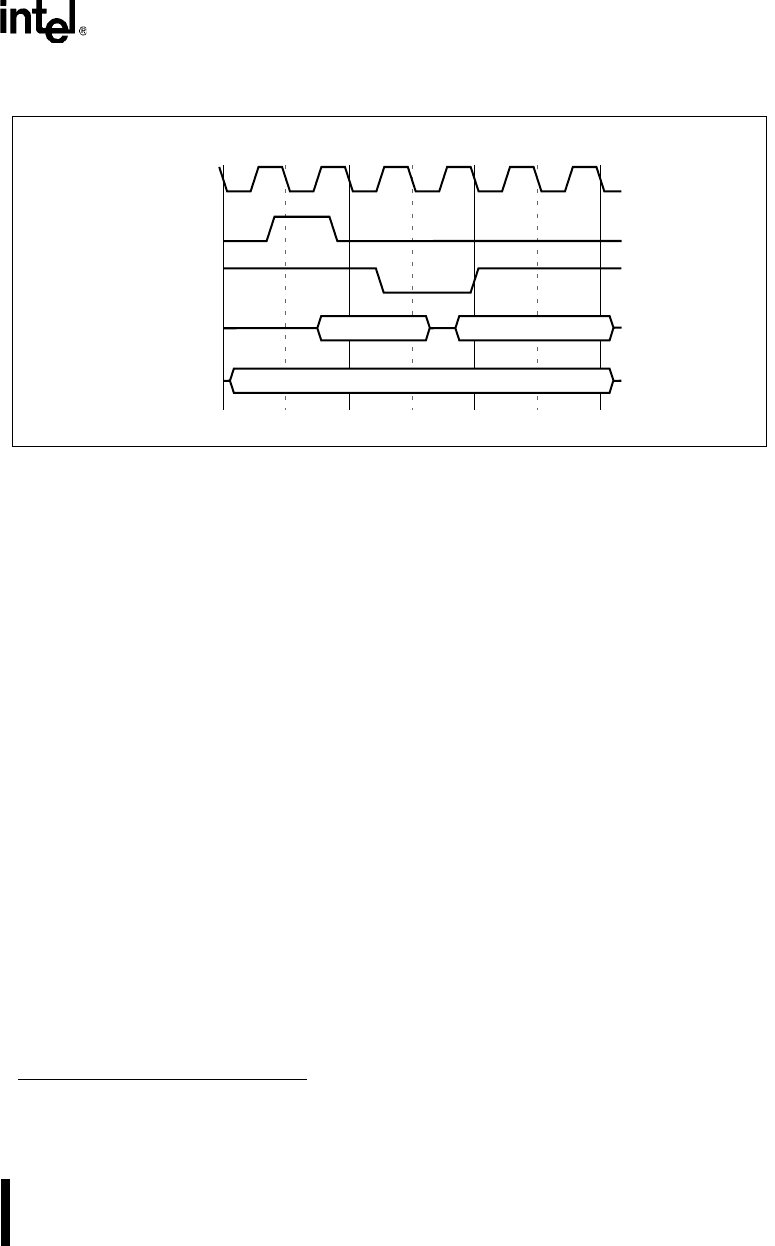

Figure 13-4. External Data Write (Nonpage Mode)

13.2.3 Page Mode Bus Cycles

Page mode increases performance by reducing the time for external code fetches. Under certain

conditions the controller fetches an instruction from external memory in one state time instead of

two (Table 13-2). Page mode does not affect internal code fetches.

The first code fetch to a 256-byte “page” of memory always uses a two-state bus cycle. Subse-

quent successive code fetches to the same page (page hits) require only a one-state bus cycle.

When a subsequent fetch is to a different page (a page miss) it again requires a two-state bus cy-

cle. The following external code fetches are always page-miss cycles:

• the first external code fetch after a page rollover†

• the first external code fetch after an external data bus cycle

• the first external code fetch after powerdown or idle mode

• the first external code fetch after a branch, return, interrupt, etc.

In page mode, the 8XC251Sx bus structure differs from the bus structure in MCS 51 controllers

(Figure 13-1). The upper address bits A15:8 are multiplexed with the data D7:0 on port 2, and the

lower address bits (A7:0) are on port 0.

† A page rollover occurs when the address increments from the top of one 256-byte page to the bottom of

the next (e.g., from FF:FAFFH to FF:FB00H).

P0

A17/A16/P2

ALE

WR#

State 1 State 2

XTAL

State 3

A2808-03

A7:0

D7:0

A17/A16/A15:8