8XC251SA, SB, SP, SQ USER’S MANUAL

A-6

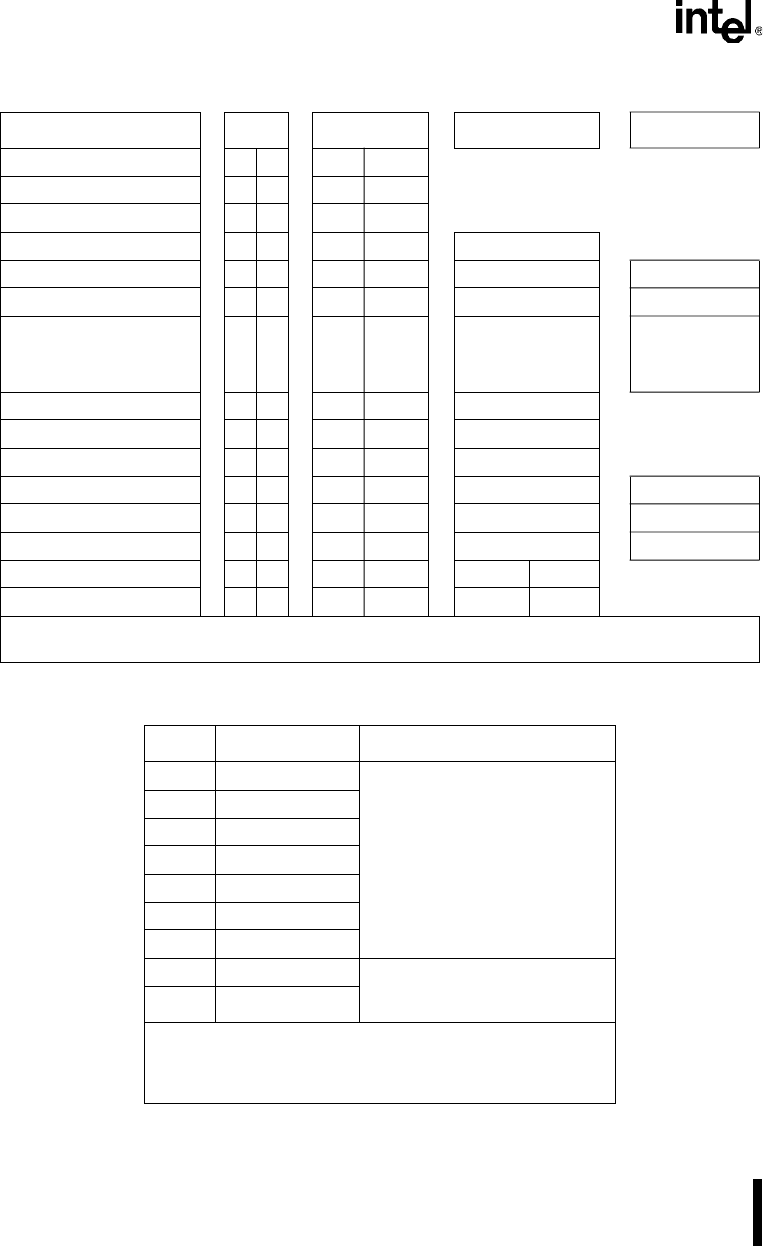

Table A-8. Data Instructions

Instruction Byte 0 Byte 1 Byte 2 Byte 3

Oper Rmd,Rms x C md ms

Oper WRjd,WRjs x D jd/2 js/2

Oper DRkd,DRks x F kd/4 ks/4

Oper Rm,#data x E m 0000 #data

Oper WRj,#data16 x E j/2 0100 #data (high) #data (low)

Oper DRk,#data16 x E k/4 1000 #data (high) #data (low)

MOV DRk(h),#data16

MOV DRk,#1data16

CMP DRk,#1data16

7

7

B

A

E

E

k/4 1100 #data (high) #data (low)

Oper Rm,dir8 x E m 0001 dir8 addr

Oper WRj,dir8 x E j/2 0101 dir8 addr

Oper DRk,dir8 x E k/4 1101 dir8 addr

Oper Rm,dir16 x E m 0011 dir16 addr (high) dir16 addr (low)

Oper WRj,dir16 x E j/2 0111 dir16 addr (high) dir16 addr (low)

Oper DRk,dir16 (1) x E k/4 1111 dir16 addr (high) dir16 addr (low)

Oper Rm,@WRj x E j/2 1001 m 00

Oper Rm,@DRk x E k/4 1011 m 00

NOTE:

1. For this instruction, the only valid operation is MOV.

Table A-9. High Nibble, Byte 0 of Data Instructions

x Operation Notes

2 ADD reg,op2

All addressing modes are

supported.

9 SUB reg,op2

B CMP reg,op2 (1)

4 ORL reg,op2 (2)

5 ANL reg,op2 (2)

6 XRL reg,op2 (2)

7 MOV reg,op2

8 DIV reg,op2 Two modes only:

reg,op2 = Rmd,Rms

reg,op2 = Wjd,Wjs

A MUL reg,op2

NOTES:

1. The CMP operation does not support DRk, direct16.

2. For the ORL, ANL, and XRL operations, neither reg nor op2

can be DRk.