C-29

REGISTERS

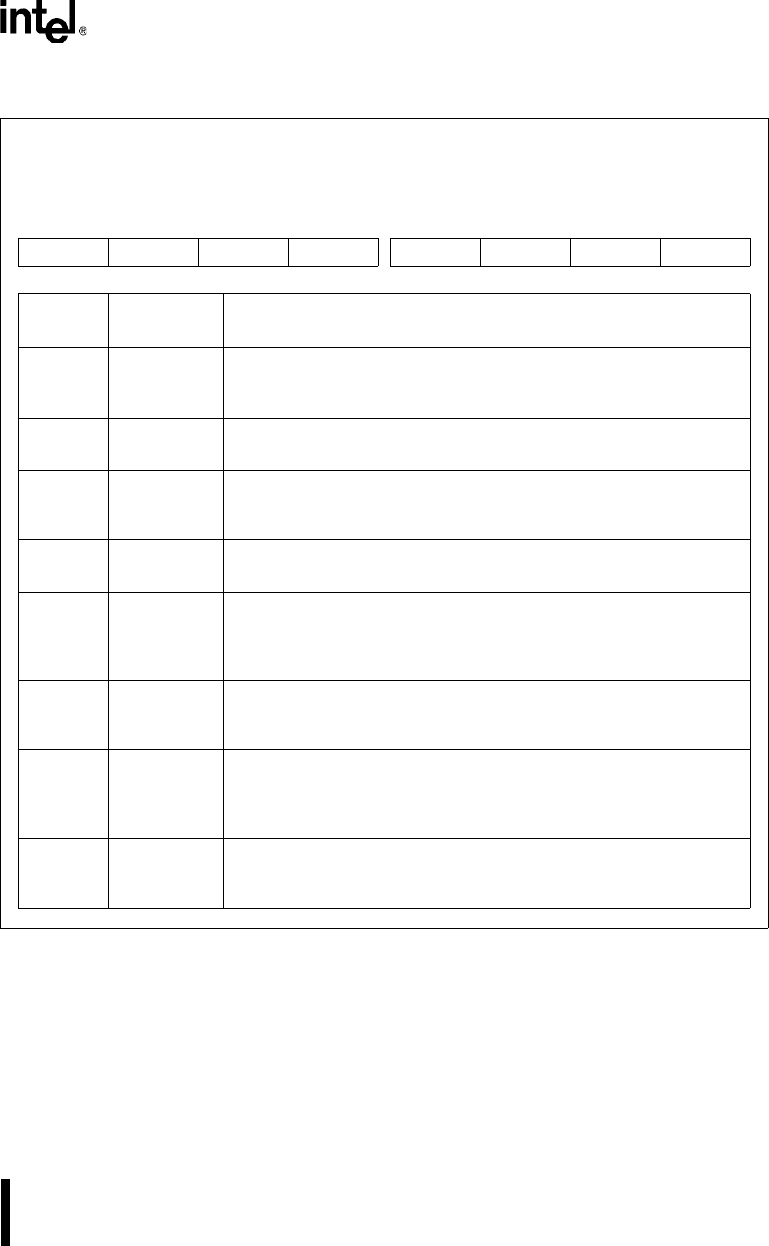

TCON

Address: S:88H

Reset State: 0000 0000B

Timer/Counter Control Register. Contains the overflow and external interrupt flags and the run control

and interrupt transition select bits for timer 0 and timer 1.

7 0

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

Bit

Number

Bit

Mnemonic

Function

7 TF1 Timer 1 Overflow Flag:

Set by hardware when the timer 1 register overflows. Cleared by

hardware when the processor vectors to the interrupt routine.

6 TR1 Timer 1 Run Control Bit:

Set/cleared by software to turn timer 1 on/off.

5 TF0 Timer 0 Overflow Flag:

Set by hardware when the timer 0 register overflows. Cleared by

hardware when the processor vectors to the interrupt routine.

4 TR0 Timer 0 Run Control Bit:

Set/cleared by software to turn timer 1 on/off.

3 IE1 Interrupt 1 Flag:

Set by hardware when an external interrupt is detected on the INT1# pin.

Edge- or level- triggered (see IT1). Cleared when interrupt is processed

if edge-triggered.

2 IT1 Interrupt 1 Type Control Bit:

Set this bit to select edge-triggered (high-to-low) for external interrupt 1.

Clear this bit to select level-triggered (active low).

1 IE0 Interrupt 1 Flag:

Set by hardware when an external interrupt is detected on the INT0# pin.

Edge- or level- triggered (see IT0). Cleared when interrupt is processed

if edge-triggered.

0 IT0 Interrupt 0 Type Control Bit:

Set this bit to select edge-triggered (high-to-low) for external interrupt 0.

Clear this bit to select level-triggered (active low).