6-13

INTERRUPT SYSTEM

6.7.2.3 Latency Calculations

Assume the use of a zero-wait-state external memory where current instructions, the ISR, and the

stack are located within the same 64-Kbyte memory region (compatible with memory maps for

MCS 51 microcontrollers.) Further, assume there are 3 states yet to complete in the current 21-

state DIV instruction when INT0# requests service. Also assume INT0# has made the request one

state prior to the sample state (as in Figure 6-7). Unlike in Figure 6-7, the response time for this

assumption is three state times as the current instruction completes in time for the branch to occur.

Latency calculations begin with the minimum fixed latency of 16 states. From Table 6-6, one state

is added for an INT0# request from external hardware; two states are added for external execu-

tion; and four states for an external stack in the current 64-Kbyte region. Finally, three states are

added for the current instruction to complete. The actual latency is 26 states. Worst-case latency

calculations predict 43 states for this example due to inclusion of total DIV instruction time (less

one state).

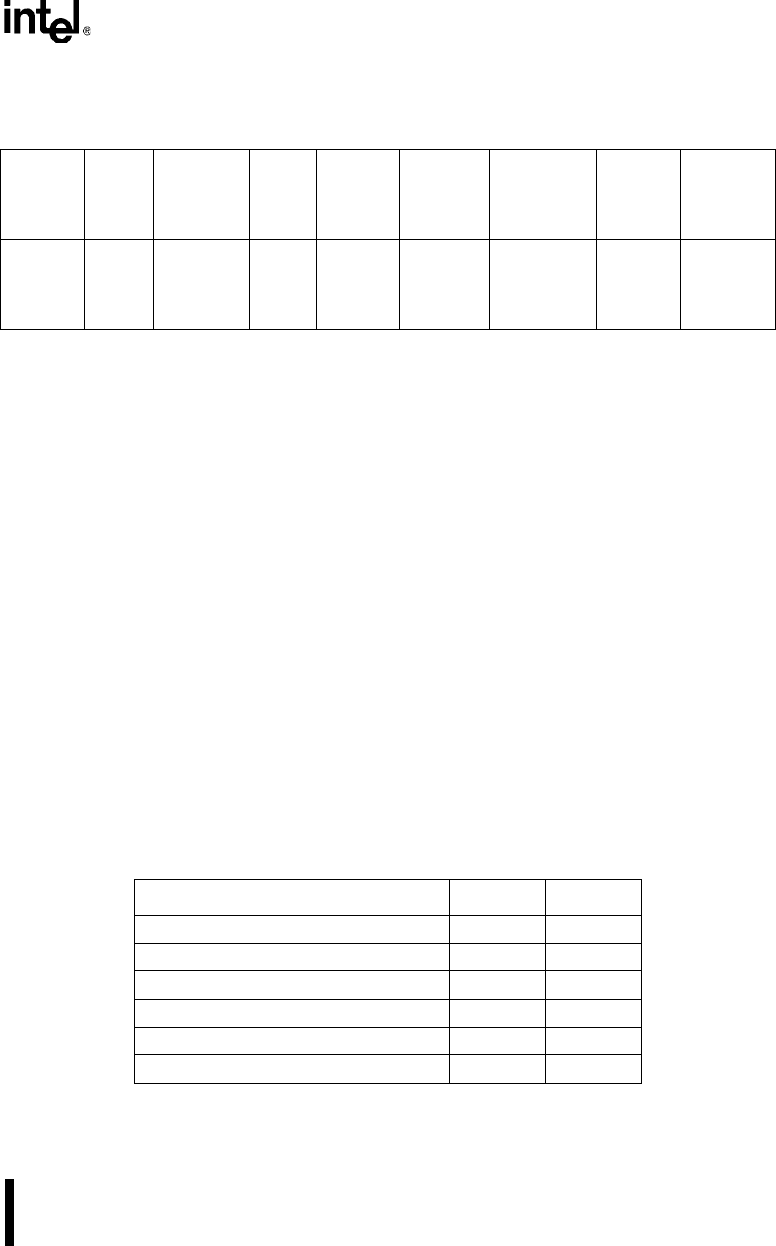

Table 6-6. Interrupt Latency Variables

Variable

INT0#,

INT1#,

T2EX

External

Execution

Page

Mode

>64K

Jump to

ISR (1)

External

Memory

Wait

State

External

Stack

<64K (1)

External

Stack

>64K (1)

External

Stack

Wait State

Number

of

States

Added

1218

1 per

bus cycle

48

1 per

bus cycle

NOTES:

1. <64K/>64K means inside/outside the 64-Kbyte memory region where code is executing.

2. Base-case fixed time is 16 states and assumes:

— A 2-byte instruction is the first ISR byte. — Internal execution

— <64K jump to ISR — Internal stack

— Internal peripheral interrupt

Table 6-7. Actual vs. Predicted Latency Calculations

Latency Factors Actual Predicted

Base Case Minimum Fixed Time 16 16

INT0# External Request 1 1

External Execution 2 2

<64K Byte Stack Location 4 4

Execution Time for Current DIV Instruction 3 20

TOTAL 26 43