8XC251SA, SB, SP, SQ USER’S MANUAL

8-16

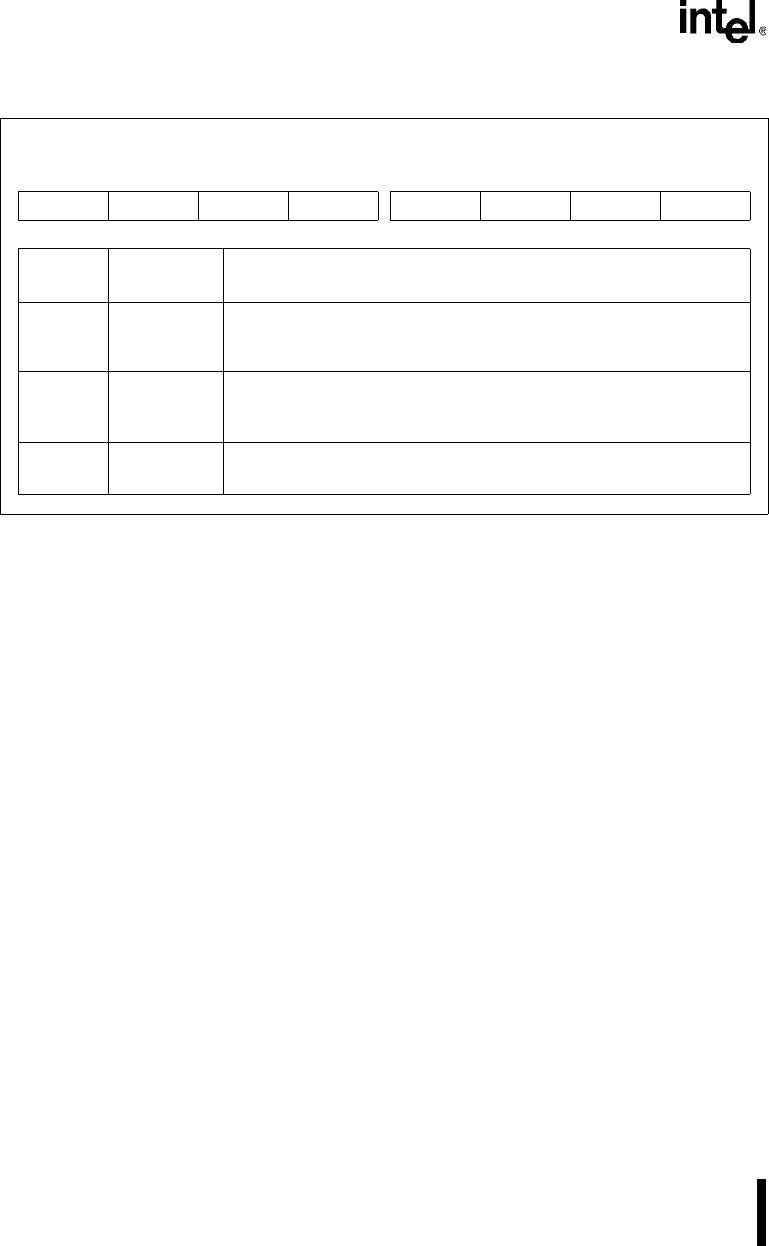

Figure 8-11. T2MOD: Timer 2 Mode Control Register

8.7 WATCHDOG TIMER

The peripheral section of the 8XC251Sx contains a dedicated, hardware watchdog timer (WDT)

that automatically resets the chip if it is allowed to time out. The WDT provides a means of re-

covering from routines that do not complete successfully due to software malfunctions. The WDT

described in this section is not associated with the PCA watchdog timer, which is implemented

in software.

8.7.1 Description

The WDT is a 14-bit counter that counts peripheral cycles, i.e., the system clock divided by

twelve (F

OSC

/12). The WDTRST special function register at address S:A6H provides control ac-

cess to the WDT. Two operations control the WDT:

• Device reset clears and disables the WDT (see section 11.4, “Reset”).

• Writing a specific two-byte sequence to the WDTRST register clears and enables the WDT.

If it is not cleared, the WDT overflows on count 3FFFH + 1. With F

OSC

= 16 MHz, a peripheral

cycle is 750 ns and the WDT overflows in 750 × 16384 = 12.288 ms. The WDTRST is a write-

only register. Attempts to read it return FFH. The WDT itself is not read or write accessible. The

WDT does not drive the external RESET pin.

T2MOD

Address: S:C9H

Reset State: XXXX XX00B

7 0

———— ——T2OEDCEN

Bit

Number

Bit

Mnemonic

Function

7:2 — Reserved:

The values read from these bits are indeterminate. Write zeros to these

bits.

1 T2OE Timer 2 Output Enable Bit:

In the timer 2 clock-out mode, connects the programmable clock output

to external pin T2.

0 DCEN Down Count Enable Bit:

Configures timer 2 as an up/down counter.