13-13

EXTERNAL MEMORY INTERFACE

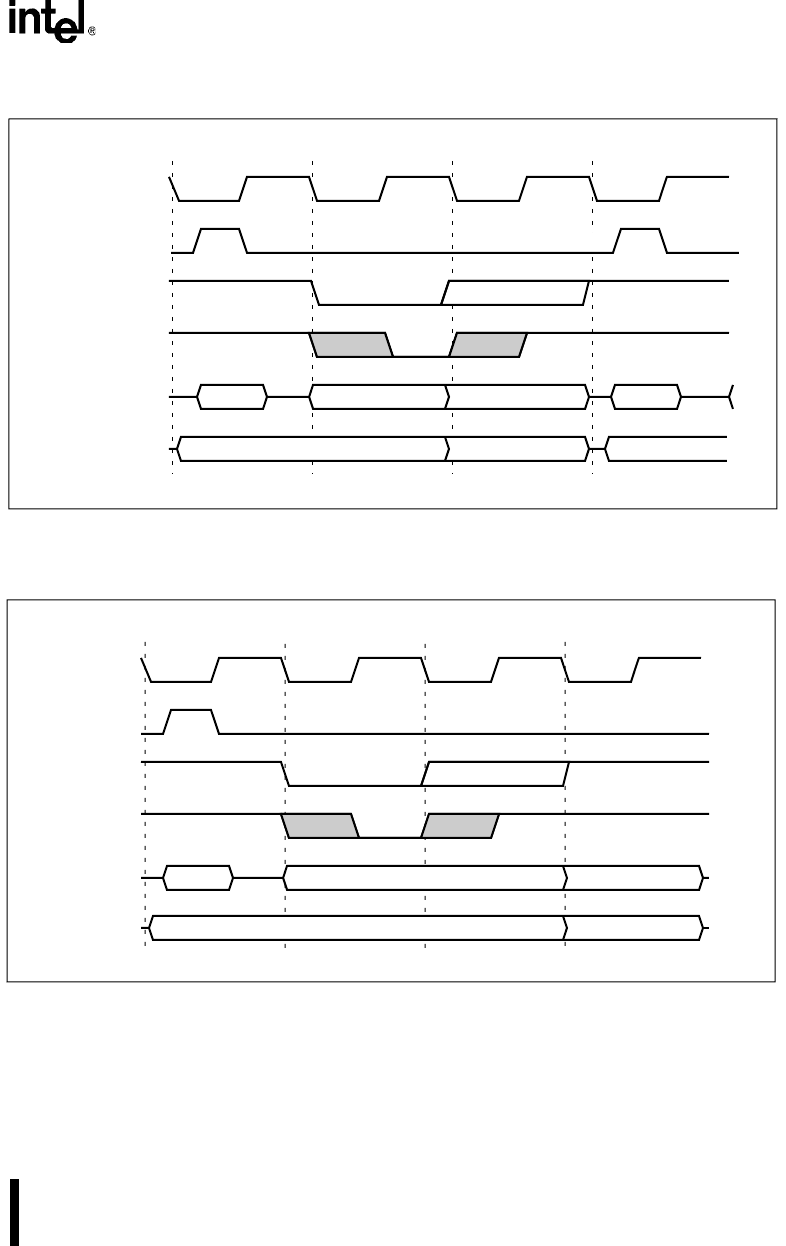

Figure 13-12. External Code Fetch/Data Read (Nonpage Mode, RT Wait State)

Figure 13-13. External Data Write (Nonpage Mode, RT Wait State)

A0-A7

WCLK

ALE

RD#/PSEN#

WAIT#

P0

P2

A8-A15

A5007-01

State 1 State 2 State 3 State 1 (next cycle)

A0-A7D0-D7 stretched

A8-A15 stretched

RD#/PSEN# stretched

A0-A7

WCLK

ALE

WR#

WAIT#

P0

P2

A5009-01

State 1 State 2 State 3 State 4

D0-D7

stretched

A8-A15 stretched

WR# stretched