8-13

TIMER/COUNTERS AND WATCHDOG TIMER

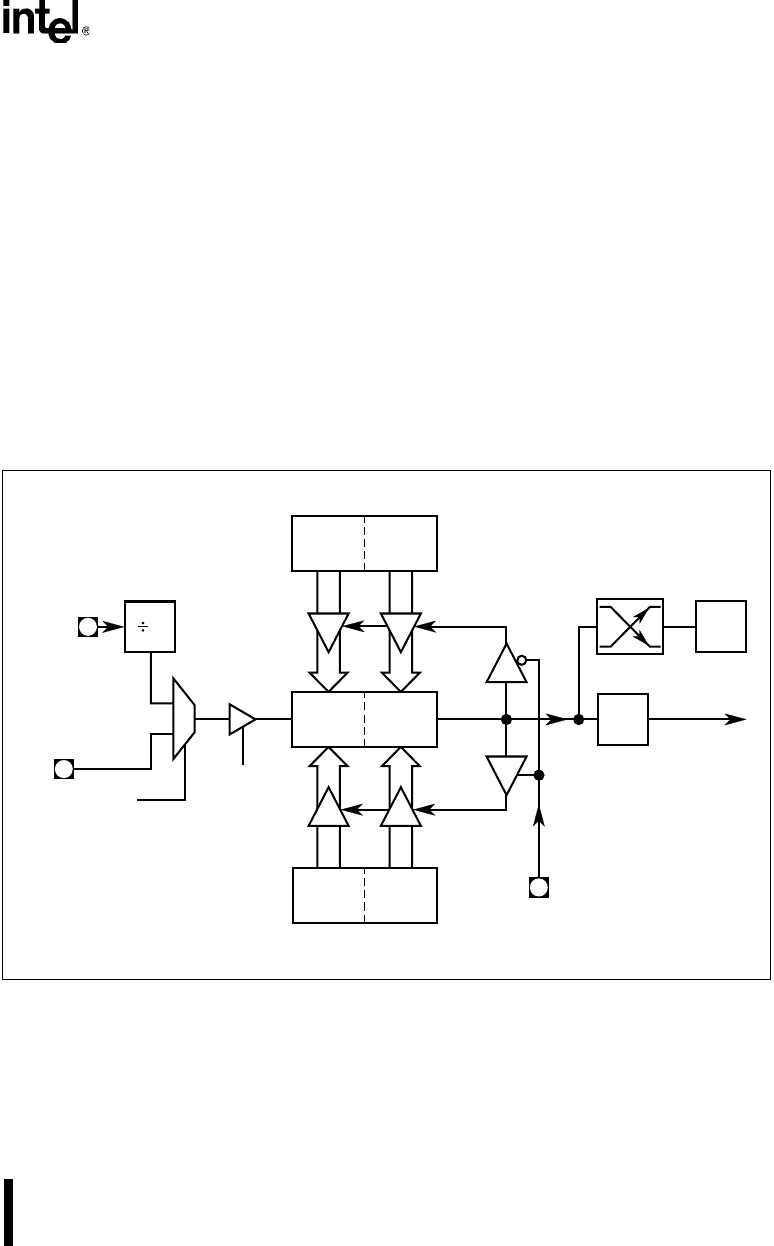

8.6.2.2 Up/Down Counter Operation

When DCEN = 1, timer 2 operates as an up/down counter (Figure 8-9). External pin T2EX con-

trols the direction of the count (Table 8-2 on page 8-3). When T2EX is high, timer 2 counts up.

The timer overflow occurs at FFFFH which sets the timer 2 overflow flag (TF2) and generates an

interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L to be load-

ed into the timer registers TH2 and TL2.

When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer

registers (TH2, TL2) equals the value stored in RCAP2H and RCAP2L. The underflow sets the

TF2 bit and reloads FFFFH into the timer registers.

The EXF2 bit toggles when timer 2 overflows or underflows changing the direction of the count.

When timer 2 operates as an up/down counter, EXF2 does not generate an interrupt. This bit can

be used to provide 17-bit resolution.

Figure 8-9. Timer 2: Auto Reload Mode (DCEN = 1)

Interrupt

Request

T2

Overflow

TR2

TH2

(8 Bits)

TL2

(8 Bits)

FFH FFH

12

T2EX

Count

Direction

1 = Up

0 = Down

TF2

EXF2

Toggle

(Down Counting Reload Value)

(Up Counting Reload Value)

RCAP2LRCAP2H

A4114-01

XTAL1

C/T2#

0

1