8XC251SA, SB, SP, SQ USER’S MANUAL

A-20

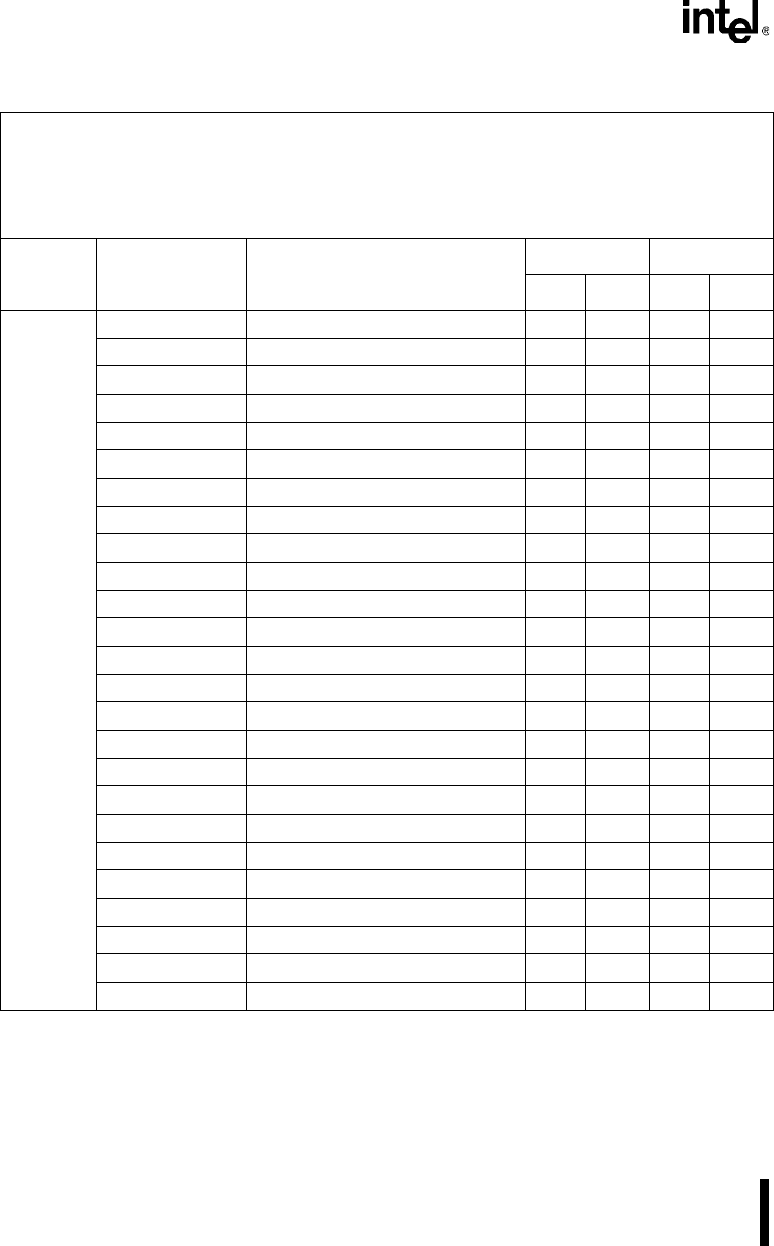

MOV

DRk,dir8 Dir addr to dword reg 4 6 3 5

DRk,dir16 Dir addr (64K) to dword reg 5 6 4 5

Rm,dir8 Dir addr to byte reg 4 3 (3) 3 2 (3)

WRj,dir8 Dir addr to word reg 4 4 3 3

Rm,dir16 Dir addr (64K) to byte reg 5 3 4 2

WRj,dir16 Dir addr (64K) to word reg 5 4 4 3

Rm,@WRj Indir addr (64K) to byte reg 4 2 3 2

Rm,@DRk Indir addr (16M) to byte reg 4 4 3 3

WRjd,@WRjs Indir addr(64K) to word reg 4 4 3 3

WRj,@DRk Indir addr(16M) to word reg 4 5 3 4

dir8,Rm Byte reg to dir addr 4 4 (3) 3 3 (3)

dir8,WRj Word reg to dir addr 4 5 3 4

dir16,Rm Byte reg to dir addr (64K) 5 4 4 3

dir16,WRj Word reg to dir addr (64K) 5 5 4 4

@WRj,Rm Byte reg to indir addr (64K) 4 4 3 3

@DRk,Rm Byte reg to indir addr (16M) 4 5 3 4

@WRjd,WRjs Word reg to indir addr (64K) 4 5 3 4

@DRk,WRj Word reg to indir addr (16M) 4 6 3 5

dir8,DRk Dword reg to dir addr 4 7 3 6

dir16,DRk Dword reg to dir addr (64K) 5 7 4 6

Rm,@WRj+dis16 Indir addr with disp (64K) to byte reg 5 6 4 5

WRj,@WRj+dis16 Indir addr with disp (64K) to word reg 5 7 4 6

Rm,@DRk+dis24 Indir addr with disp (16M) to byte reg 5 7 4 6

WRj,@DRk+dis24 Indir addr with disp (16M) to word reg 5 8 4 7

@WRj+dis16,Rm Byte reg to Indir addr with disp (64K) 5 6 4 5

Table A-24. Summary of Move Instructions (Continued)

Move (2) MOV <dest>,<src> destination ← src opnd

Move with Sign Extension MOVS <dest>,<src> destination ← src opnd with sign extend

Move with Zero Extension MOVZ <dest>,<src> destination ← src opnd with zero extend

Move Code Byte MOVC <dest>,<src> A ← code byte

Move to External Mem MOVX <dest>,<src> external mem ← (A)

Move from External Mem MOVX <dest>,<src> A ← source opnd in external mem

Mnemonic <dest>,<src> Notes

Binary Mode Source Mode

Bytes States Bytes States

NOTES:

1. A shaded cell denotes an instruction in the MCS

®

51 architecture.

2. Instructions that move bits are in Table A-26 on page A-23.

3. If this instruction addresses an I/O port (P

x

,

x

= 0–3), add 1 to the number of states.

4. External memory addressed by instructions in the MCS 51 architecture is in the region specified by

DPXL (reset value = 01H). See section 3.1.1, “Compatibility with the MCS® 51 Architecture.”